# CB PLL DATA BOOK

Lou Franklin

#### A Repair & Modification Reference

Includes American, British, & European CB Radios AM, FM, & SSB Circuits

#### **CONTENTS**

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Section I - BASIC PLL BACKGROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5          |

| Frequency Mixing — Intermediate Frequencies — SSB Mixing — The "Odd" British Channels — The PLL for FM Use — A Basic Crystal Synthesizer — Equivalent PLL Synthesizer — Elements of The PLL System — Reference Oscillator & Divider — Programmable Divider — Phase Detector — Loop Or Low-Pass Filter — Voltage-Controlled Oscillator — The Loop Mixer — The 5.12 MHz Loop Mixing Output — Current Technical Trends — Special Chip Functions — The T/R Shift — Misprogram Code Pin — Frequency Select Pin — Automatic Ch. 9/Ch. 19 Command — Scanning Interface |            |

| Section II - BACKGROUND FOR MODIFICATION METHODS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 32       |

| Typical Synthesizer Circuit — Binary Programming — VCO Circuit — Loop Mixing — Phase Detector Correction — Receiver IFs — Transmitter Section — Truth Charts — BCD Programming — Presettable Dividers — Multimode Programming — Controlling Program Pins — ROM Code Converters — Other ROM Variations — Loop Mixer Modifications — CB-to-Ham Conversion Problems — Sample Modification — Crystal Switching Methods — External Crystal Oscillators — Crystal Sources — The Reference Oscillator Crystal — The Impossible Chips                                   |            |

| Section III - PLL CHIP SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 61       |

| Inside The Mysterious PLL Chip — Explanation of Pin Functions — N-Codes of Newer ROM Chips                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

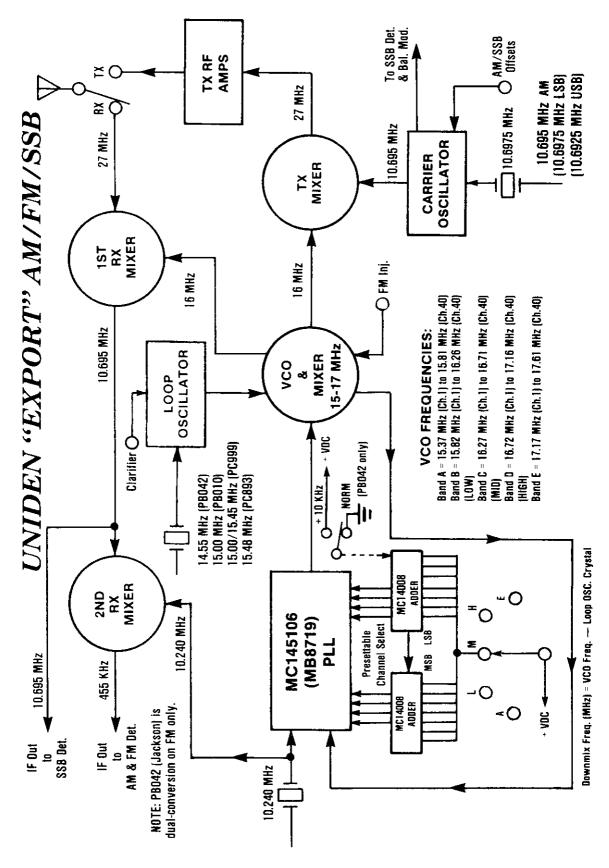

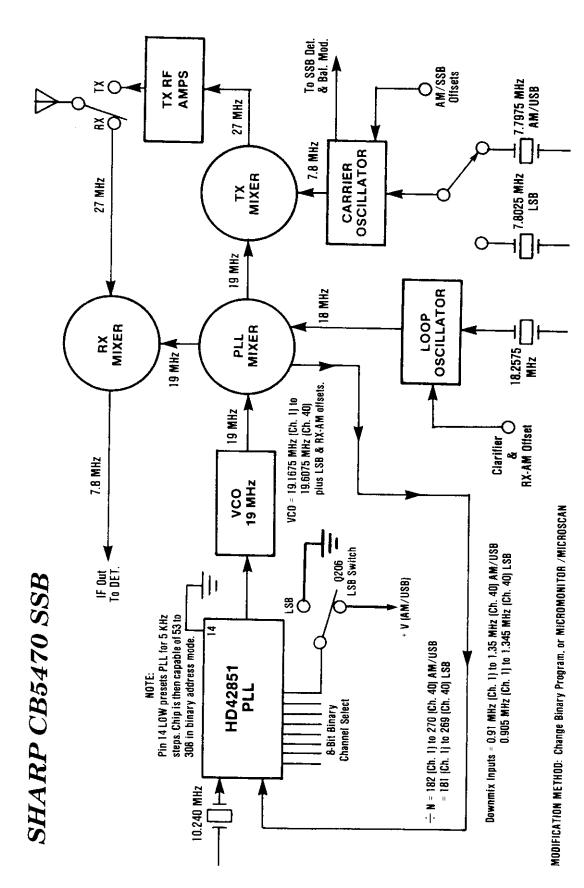

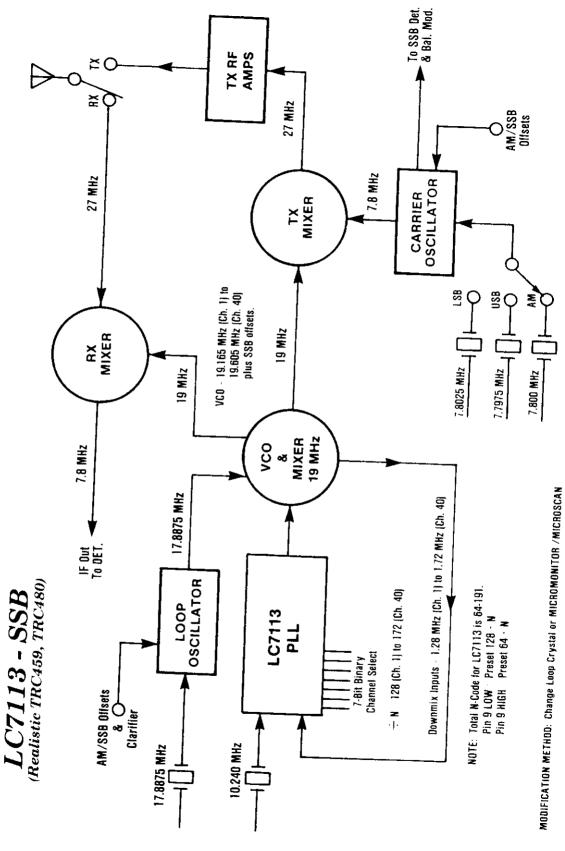

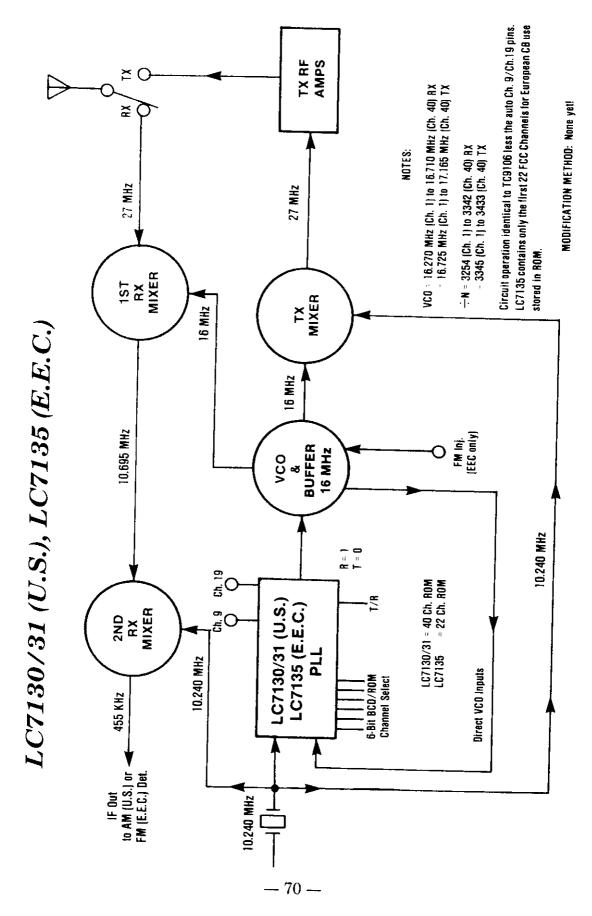

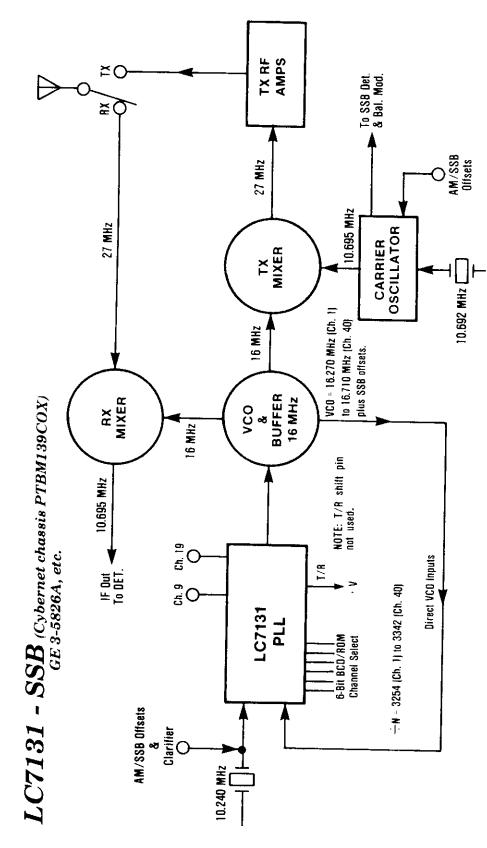

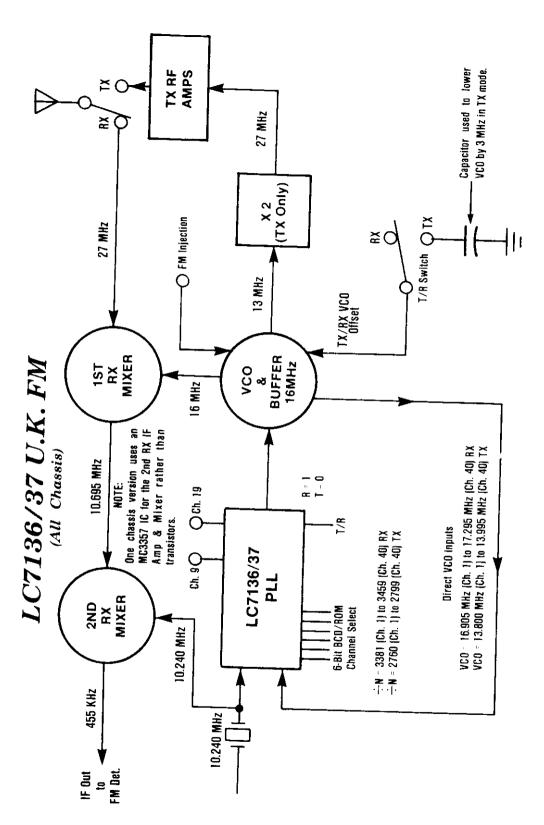

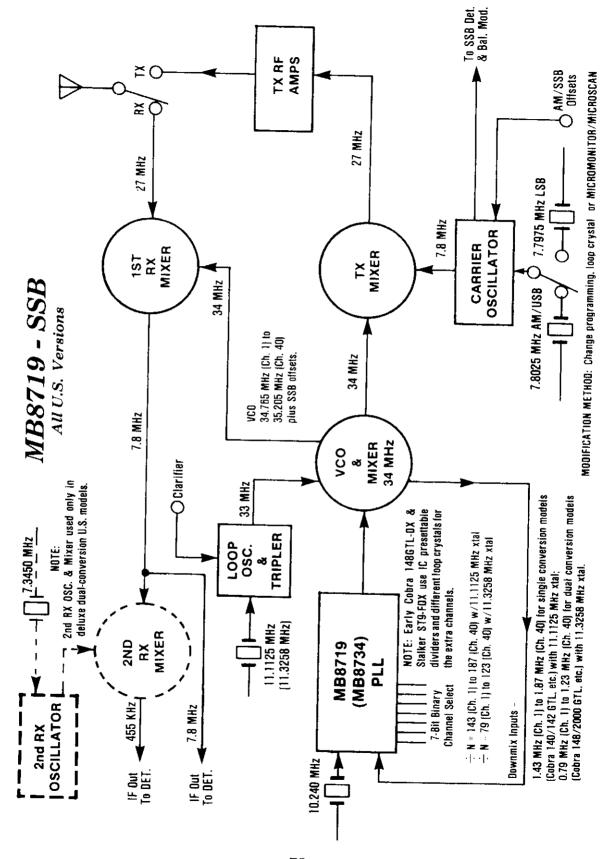

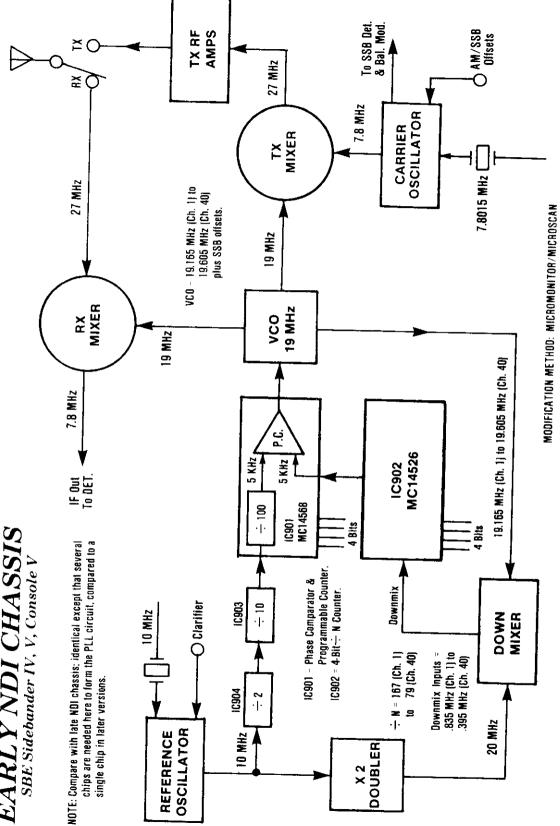

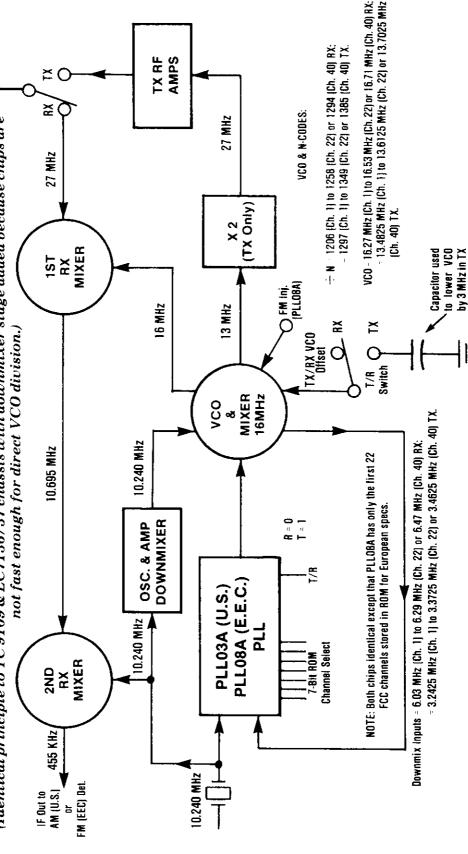

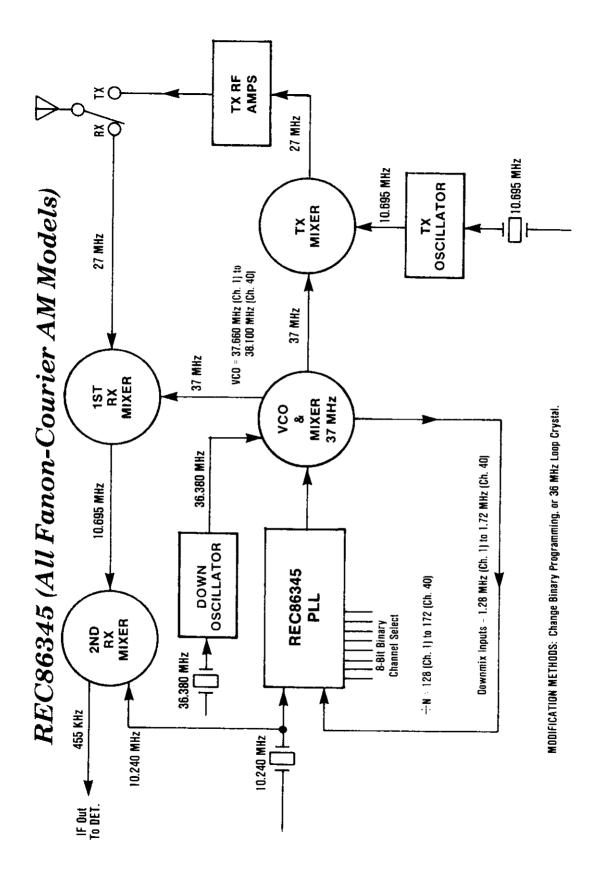

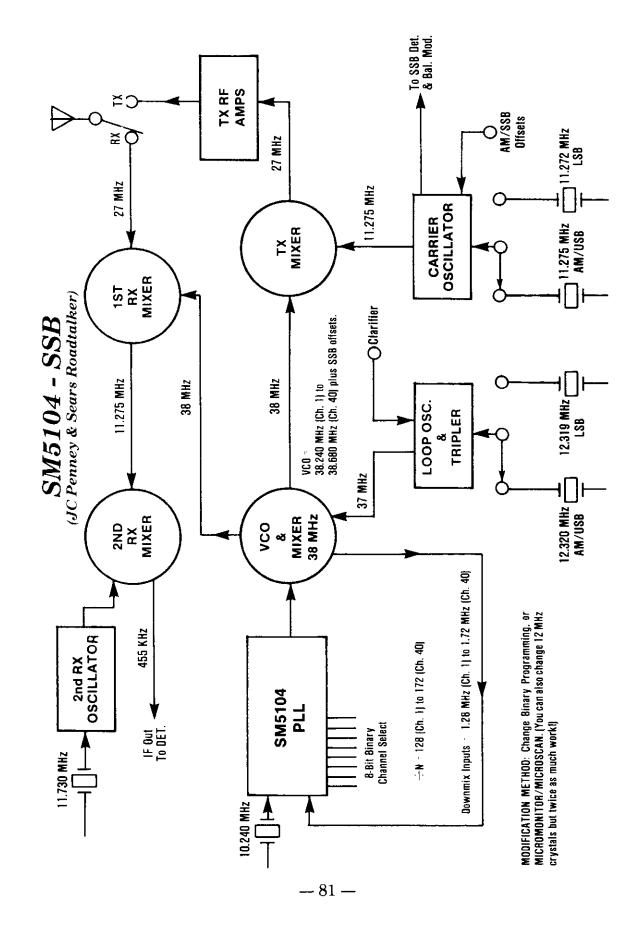

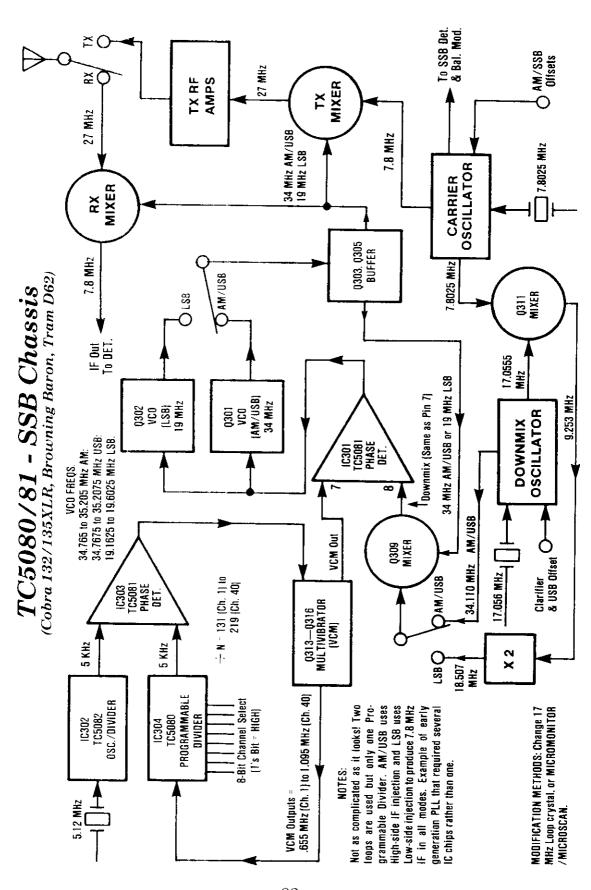

| Block Mixing Diagrams (Pages 67-92):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

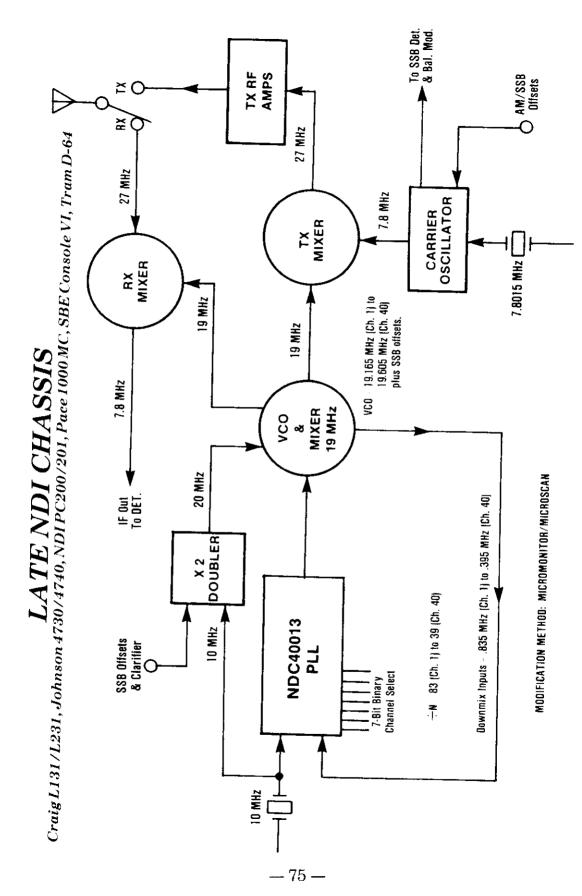

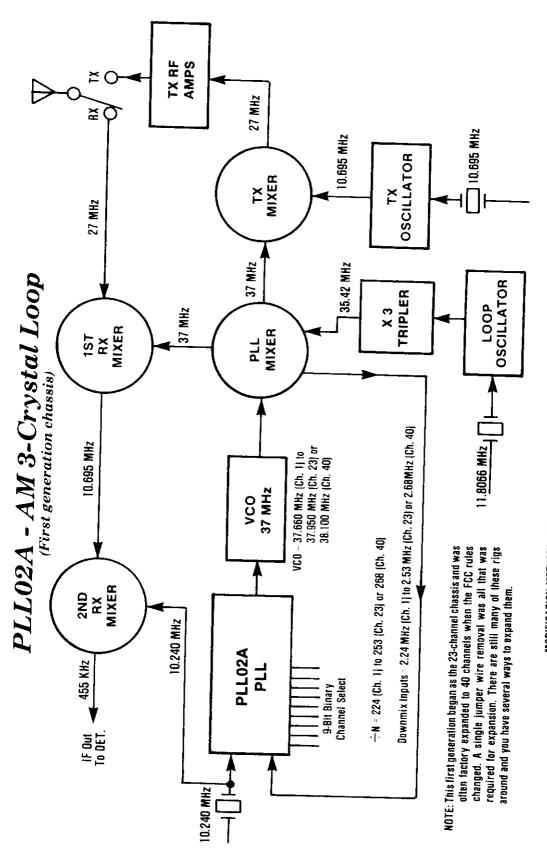

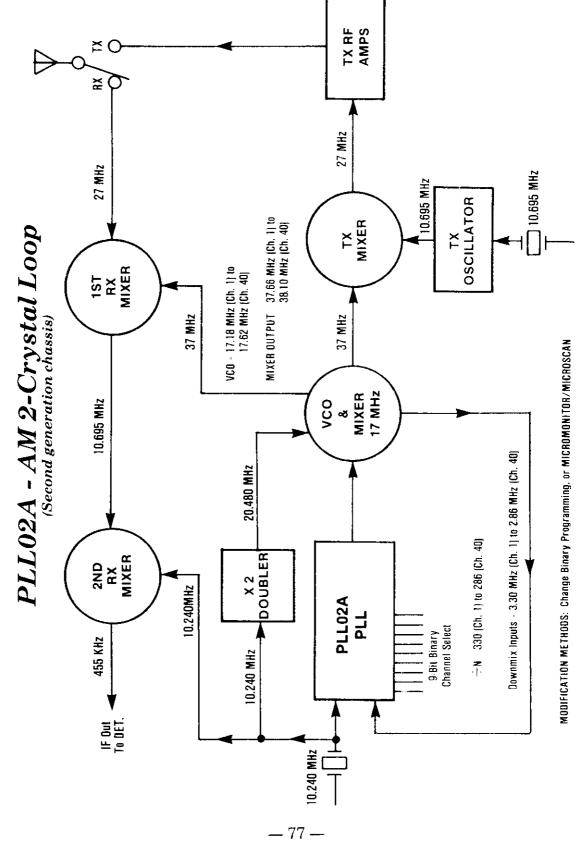

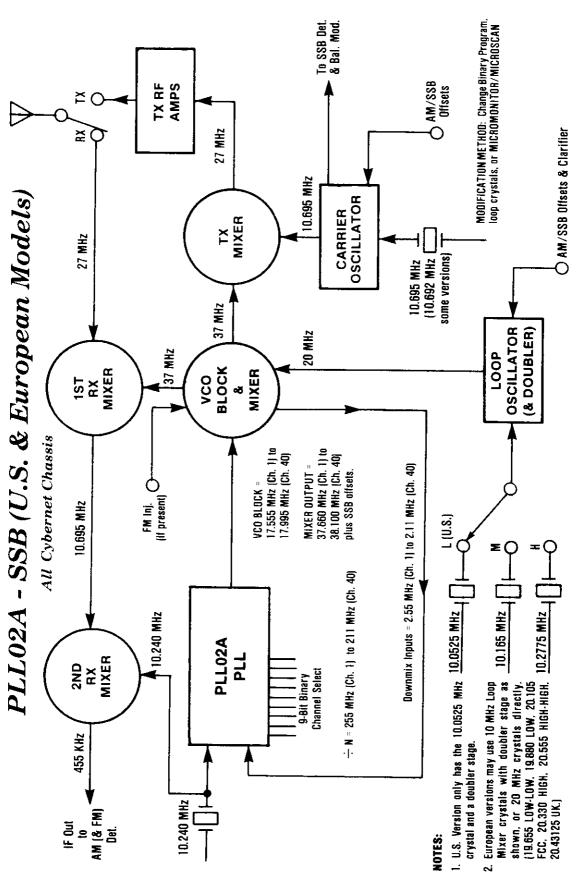

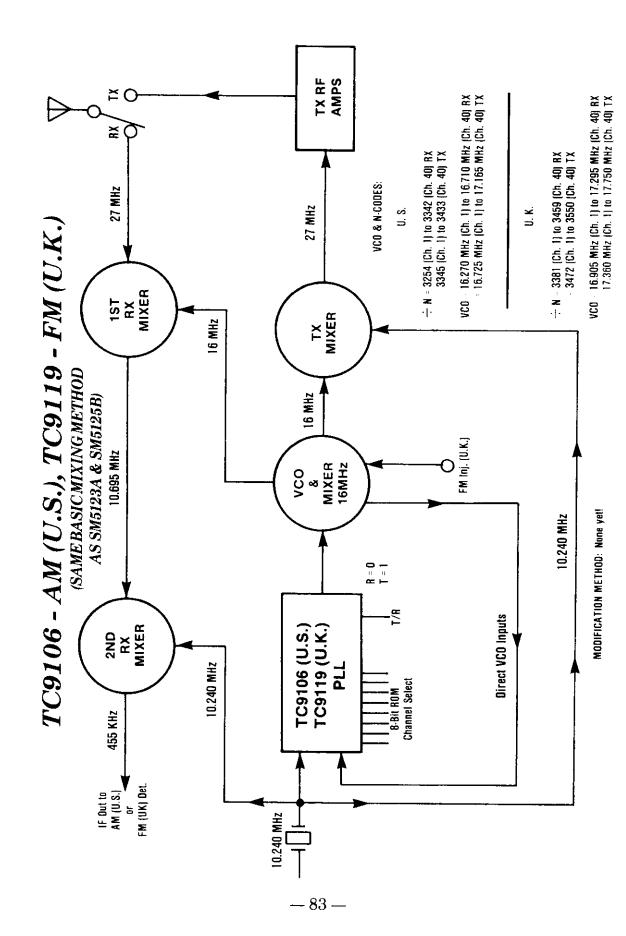

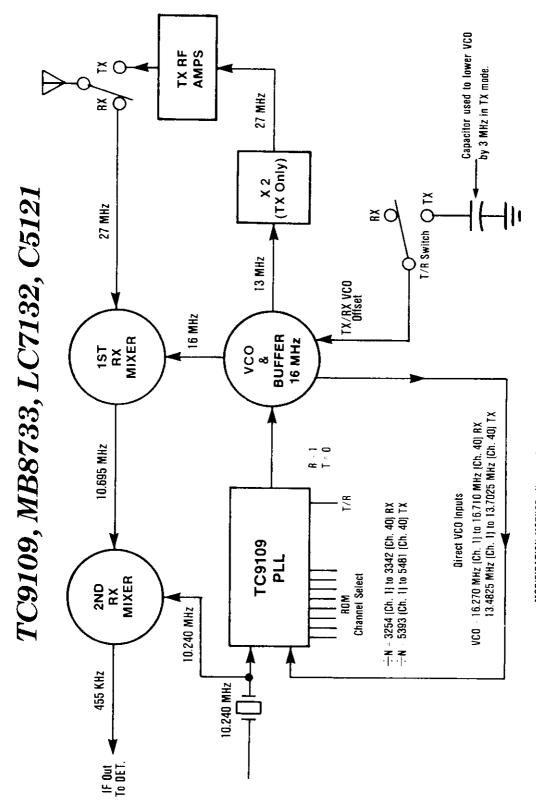

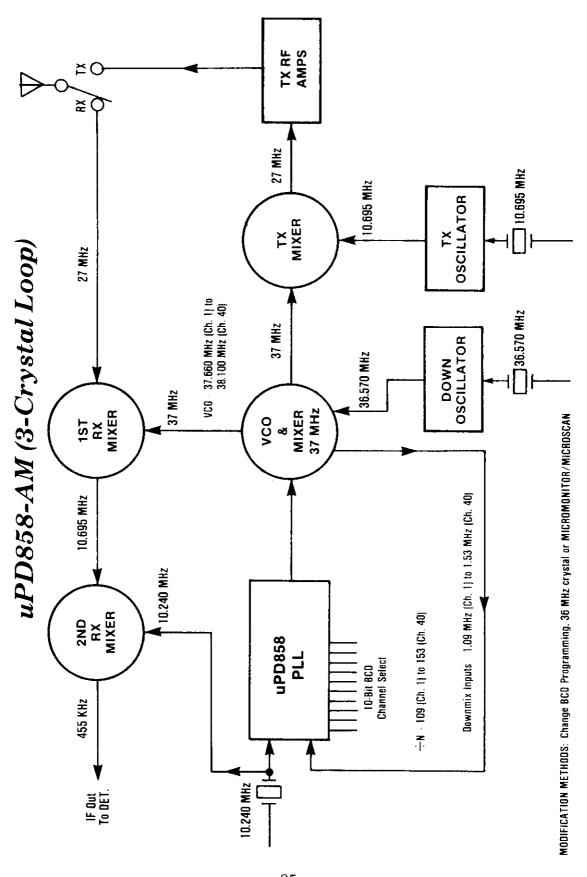

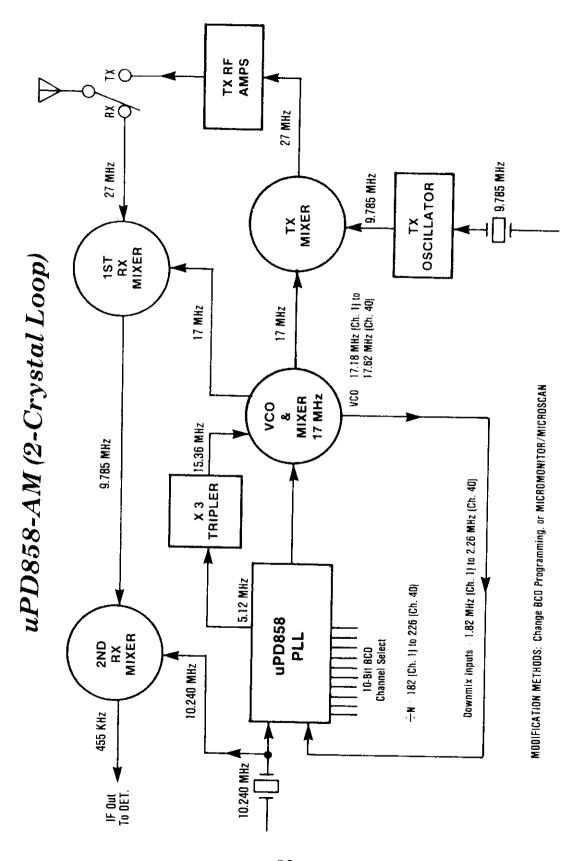

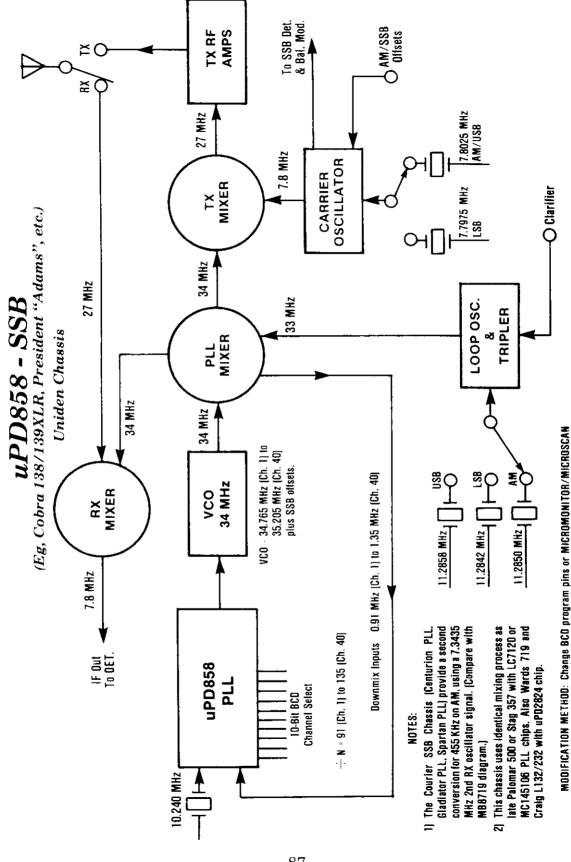

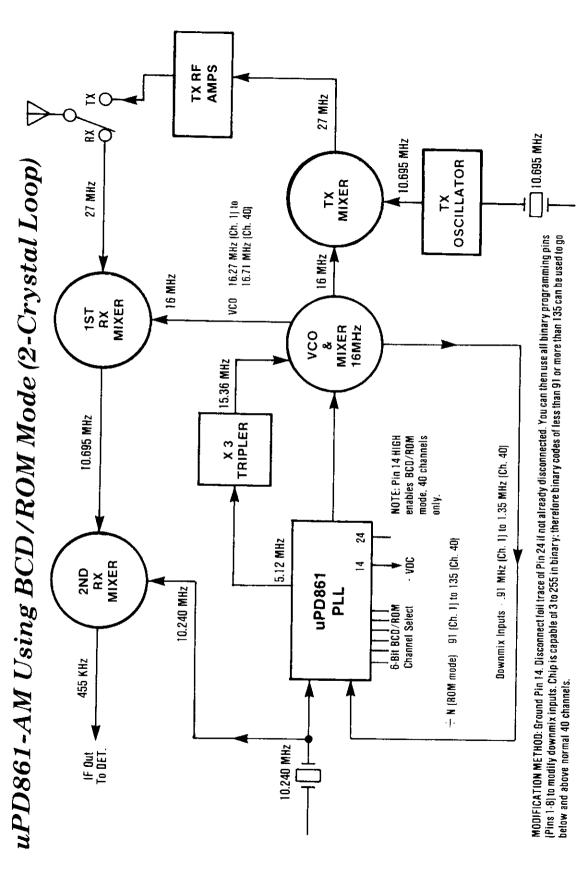

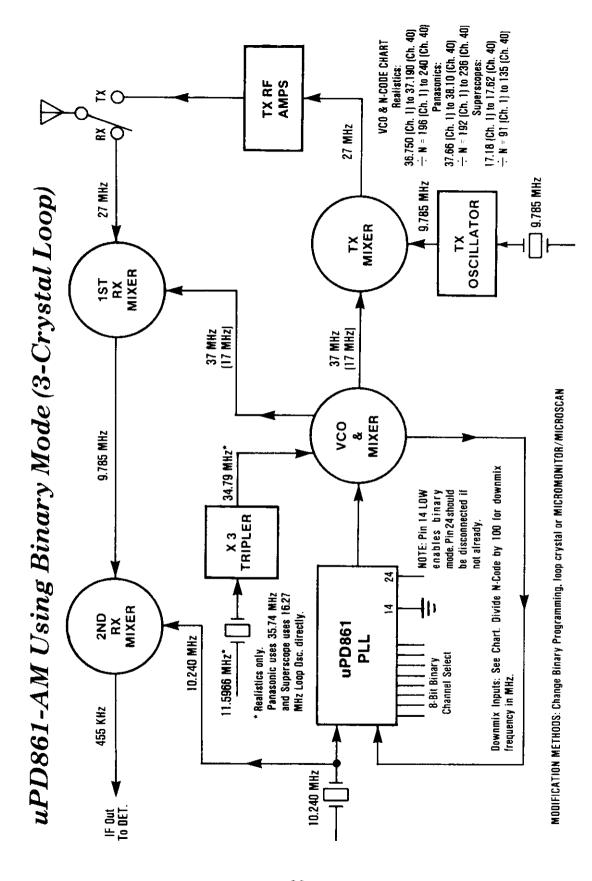

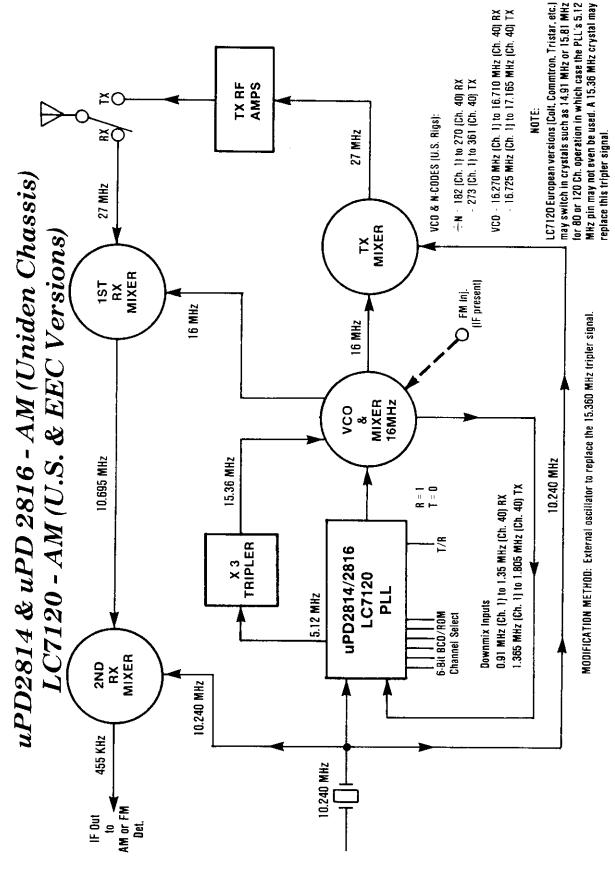

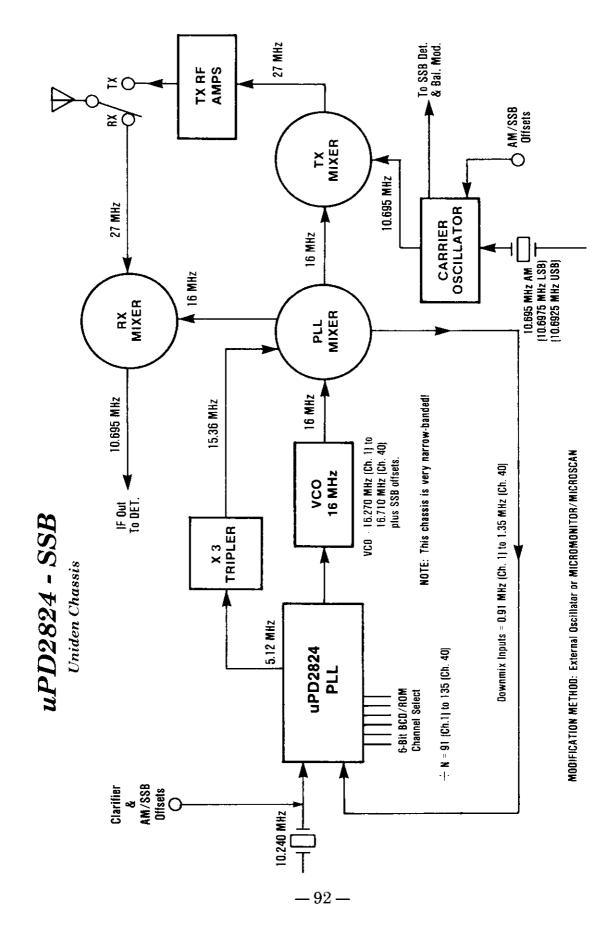

| Uniden "Export" SSB — Sharp CB5470 — LC7113 SSB — LC7130/31/35 — LC7131 SSB — LC7136/37 — MC8719 SSB — NDI Early — NDI Late — PLL02A AM 3-Crystal — PLL02A AM 2-Crystal — PLL02A SSB — PLL03A/08A — REC86345 — SM5104 SSB — TC5080/81 SSB — TC9106/9119 — TC9109/MB8733/LC7132/C5121 — uPD858 AM 2-Crystal — uPD858 AM 3-Crystal — uPD858 SSB — uPD861 AM ROM — uPD861 AM Binary — uPD2814/2816/LC7120 AM — uPD2816 SSB — uPD2824 SSB                                                                                                                           |            |

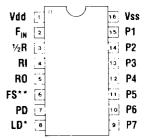

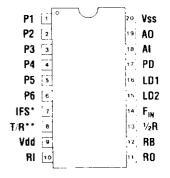

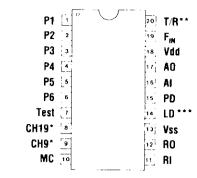

| Pin Functions ((Pages 93-107):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

| C5121 — CCI3001 — CCI3002 — HD42851 — LC7110 — LC7113 — LC7120 — LC7130/31/35/36/37 — M58472 — M58473 — MB8719/8734 — MC145106 — MC14568/14526 — MM55108 — MSC42502 — MSM5807 — MSM5907 — NDC40013 — NIS7261A — NIS7264B — PLL02A — PLL01A — PLL03A/08A — REC86345 — SM5104 — SM5107 — SM5118 — TC5080 — TC9102 — TC9103 — TC9106/9119 — TC9109/MB8733 — uPD858 — uPD861 — uPD2810 — uPD2812 — uPD2814 — uPD2816 — uPD2824                                                                                                                                      | ,<br>,     |

| LATE ADDITIONS: LC7132, SM5123A, SM5124A  LATE ADDITION: CPI Chassis Block Mixing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 108<br>109 |

#### INTRODUCTION

The Phase-Locked-Loop or "PLL" Frequency Synthesizer used in CB radios is a marvelous device. It can generate all the signals needed to run a complex transceiver, is more accurate than crystal control, and more reliable because fewer parts are needed. However, understanding its operation seems to cause a lot of anxiety among CB operators as well as professional technicians. It's the purpose of this book to explain in the simplest, most non-technical terms possible how the PLL works. Anybody interested in the technical side of CB radio should find it quite helpful. I've tried to write this for both the casual CB hobbyist and the professional serviceman.

CB radio is now a worldwide hobby. As an American who's seen it change from vacuum tubes to transistors, from crystal synthesizers to PLL synthesizers. I'm in a unique position to explain the PLL's evolution. While many of the circuits and IC "chips" detailed here are actually obsolete now, there are still a lot of those radios out there needing repair! And since most countries have limited CB operation to only 18, 22, or 40 channels, a lot of interest these days is in knowing how to expand a CB rig to cover more than the "legal" channels or frequencies. Many of the older rigs are actually much better for this purpose. There is also a lot of interest among ham radio operators in converting the CB into a 10-Meter Ham rig. I will explain in these pages how PLL repairs and modifications are approached. In many cases the changes are quite simple; it's no accident that a lot of American and European transceivers using certain PLL circuits are so popular even today. On the other hand, you may be very disappointed to find out that the most recent generation of IC chips for U.S., U.K., and European CBs were designed to be almost completely non-modifiable. Better keep that older rig if you have one!

#### **BRIEF HISTORY & DEVELOPMENT**

The main reason for the development of PLL synthesizers was the American CB service expansion from 23 to 40 channels in 1976. Until then CBs used a method of frequency generation called "crystal synthesis" or "crystal-plexing". By electronically combining the signals of 2 or 3 quartz crystal oscillators in a common "mixer", all the various Receive/Transmit signals (which are normally not the same) could be created with only 12 or 14 crystals for AM and a few more for SSB. This was a great savings in cost, circuit complexity and space, because otherwise at least 46 different quartz crystals would be needed,

one pair per channel. There wasn't enough quartz left in the world to give it all to the CB manufacturers; they had to leave some for all those Seiko wristwatches!

With CB interest growing very rapidly, new methods were required because of the increased number of legal channels. Manufacturers had to figure out how to generate a large number of signals with a minimum of parts, space, complexity, and of course, cost. The answer was the PLL synthesizer. By the time the American FCC announced its CB expansion, "digital" electronic synthesizers were already well along. In fact the last generation of 23-channel U.S. equipment had already begun to use PLL techniques rather than crystals. Those first circuits were very complicated because they required as many as 9 discrete Integrated Circuit (IC) silicon chips. Soon more and more electronic functions were crammed into a smaller chip space. Today's PLL transceiver can perform all the needed functions of channel selection and signal generation using only a single LSI ("Large-Scale-Integration") device and a handful of external parts. As we'll see, this fact is both a blessing and a curse: Good because it increases reliability and keeps radio prices affordable, but bad because the darn bugs make modifications even harder!

The FCC and other authorities quickly found that because of the unexpected popularity of CB, with millions of people all competing for the same channels, the use of illegal and unauthorized frequencies was becoming the rule rather than the exception, and this is basically the situation today. Technicians soon discovered that the first generations of PLL rigs were simple to modify. The FCC then changed its rules to require CB manufacturers to use special PLL chips to prevent this. Since Australia, Holland, Britain, and other countries had legalized CB long after the U.S., their governments took the hint and started off directly with the more secure chip circuits. However through various legal loopholes, certain makes and models of CBs in the U.S. and other countries are still allowed to be imported using the "good" PLL chips, and this subject will be covered in great detail later.

In all fairness I should mention that the newest chips are capable of some interesting features not found in earlier generations. For example, automatic command of the Channel 9 Emergency Channel or Channel 19 Road Information Channel, scanning, memory, keyboard control, greater reliability, etc. This is basically where the state-of-the-art in PLL technology is today, and there is little more that governments can do to prevent any determined radio hobbyist from modifying a rig if he really wants to. I think it's safe to assume that information in this book detailing operation of the latest PLL devices will be accurate for many years to come. And since there are still millions of older rigs out there

#### **BOOK ORGANIZATION**

I've divided this book into three general sections. The first section describes basic PLL theory in "building block" form. We'll start with the simplest chips and proceed to the most complex, in chronological order because that's the way they have evolved. In this way, you'll begin to understand how the various IC changes affect servicing and modification. I'll assume that you have very little electronic knowledge, even though some of you may be very wellinformed about other areas of CB electronics. The PLL circuits will only be illustrated in "black box" or block diagram form to keep things really simple. For example, a transistor switching circuit will be represented symbolically as a simple switch. Components like resistors, capacitors. etc. will rarely be shown at all unless very essential to the discussion. This way you'll never have to worry that you've gotten in over your head! Specific radio theory regarding AM, FM, or SSB communications not directly related to the PLL are left up to you for further study if interested. Some very basic radio theory must be included, but I've tried to keep it very uncomplicated. Since I want everybody to learn something about this subject, some areas are oversimplified, and I ask that you professional technicians out there have a little patience if something seems obvious to you.

The second section deals with modification methods as they apply to different generations of PLLs. We'll be discussing such things as Truth Charts, programming in binary, BCD and ROM, Loop Mixers, external oscillators, and tips on how to attack the various types of PLL circuits successfully.

The last section shows technical specs and block diagrams of the chips and circuits themselves. I've included every known chip of any importance. (There were a few very old chips that never lasted long enough to bother discussing.) To my knowledge this is the only book ever published devoted entirely to the subject of CB PLLs. Along with the chip pin diagrams is included a list of every radio make and model using that chip which was known at press time. Since several groups of chips work the same way, I've also included sample Truth Charts typical of such groups. I've tried to include special notations when a chip contains some unusual feature you should know about. All the specific pin functions were gathered from manufacturers' spec sheets, SAMS Fotofacts and other service manuals, and personal experience,

and are accurate to the best of my knowledge.

If you don't find your particular rig model included here, chances are that it's identical to some other rig, since there are basically now three Far East companies (Cybernet, Uniden and Maxon) that make 99% of the world's CB radios anyway. One particular chassis may be sold under dozens of brand names as most of you already know. For certain well-known chassis, I've included specific PC board numbers so that you might possibly identify an unknown rig by that number.

My two trips to England and Europe in 1981 to study the CB situation there helped greatly in gathering the special circuit information found in these pages. Most Americans will never see the "export" models of their favorite radios; information on the addition of another 80-120 channels and FM should help your own modification attempts when you see how they're done commercially. Information on the European versions of popular American rigs, as well as the newest "legal" U.K.-FM rigs, arrived just in time to appear in this book so that this is truly an international reference work. By press time, thousands of "export" rigs like the Cobra 148GTL-DX, Palomar 2400, Superstar 3600/3900, Galaxy 2100/Super Galaxy, and Ranger AR3500 had arrived in the U.S., and are included in Section III. (We have schematics on most of these if you need one.) In addition, the British CB system has changed over to the American FCC channel assignment. So UK radios are now using the American PLL chips anyway.

Obviously it's very difficult (and expensive!) to continuously update a book like this as new models appear, but the basic information for understanding any PLL circuit you'll ever see can be found here. I've personally managed to catalog literally thousands of makes and models over many years by the use of SAMS Fotofacts, factory service manuals, and schematics sent to me by my readers. I'm always anxious to add new radio models to my files for possible future revisions and to help my readers identify a specific chassis or PLL circuit. Photocopies of rig circuit diagrams are always appreciated. I welcome your comments and suggestions and hope this book helps you.

Good luck in the Battle Of The PLL!

Lou Franklin, K6NH "Supersparks"

Phoenix, Arizona, U.S.A.

# **SECTION I**

## BASIC PLL BACKGROUND

#### FREQUENCY MIXING

This principle is so basic to radio theory, whether AM, FM, or SSB, that it must be discussed briefly before proceeding further. The reason is because mixing or "conversion" is a process that requires two or more signals, and if there are no longer any crystals used to provide such signals, we have to find them somewhere! And that "somewhere" is in the PLL circuit.

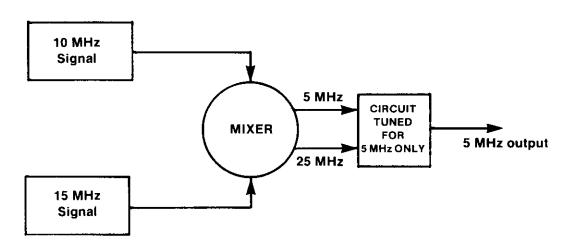

Whenever two signals are mixed together electronically, the result is two new frequencies in addition to the originals. These new frequencies are nothing more than the sum and difference of the original two, as seen in Figure 1. In this example, by mixing a 10 MHz and a 15 MHz signal together, the result will be 10 MHz, 15 MHz, 5 MHz (15 MHz - 10 MHz) and 25 MHz (15 MHz + 10 MHz). By then passing the signals through a selectively tuned circuit, only one of the mixing products will remain and the other will be rejected. The mixing process is important in PLL circuits because it provides other signals required to operate the radio that have nothing to do with the actual channel generation. Of course these other signals could be generated by individual crystal oscillators or tuneable oscillators, but this adds cost and complexity to the radio. The first generations of PLL circuits did use up to 6 individual crystal oscillators but they've now evolved to the point where a single 10.240 MHz crystal is all that's needed, at least for AM or FM.

FIGURE 1. BASIC SIGNAL MIXING PROCESS

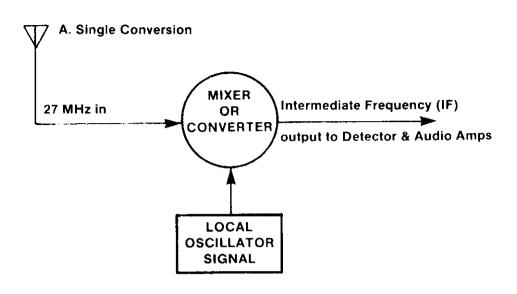

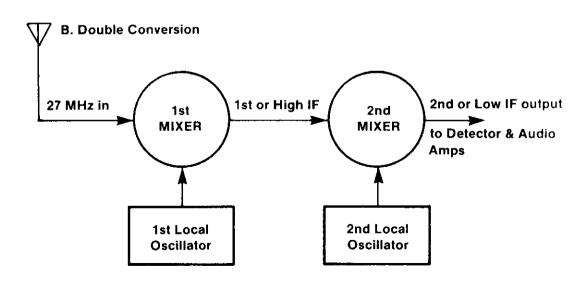

Why is the mixing process so important? The reason is because most of the signals needed in a 27 MHz CB rig are too difficult to process directly and economically while trying to maintain good performance. The CB/10M Ham band is considered a rather high frequency, and it's much better to convert a 27 MHz signal down to some lower frequency where the various Receive/Transmit circuits won't be so touchy. You've probably seen the terms "Single-conversion" or "Double-conversion" applied to receivers; this means that the 27 MHz signal is "converted", "mixed", or "heterodyned" down once or twice to a lower frequency that's easier to process. A typical AM or FM CB rig is generally of the "dual-conversion" type. For SSB, a single conversion is all that's needed but since there are no CB rigs having only SSB capability, the majority of multimode transceivers use dual conversion for AM and FMonly, with the SSB circuits using only a single conversion. (Singleconversion is quite acceptable for SSB because the T/R signals are passed through a very sharp crystal filter, typically cut near 7.8 MHz, 10.695 MHz, or 11.275 MHz.) By converting signals up or down and passing them through sharply-tuned circuits, it's much easier to get good performance, especially in receivers. The more tuned circuits, the more selectivity and sensitivity during reception, and the more reduction of unwanted "spurious" signals during transmission.

#### INTERMEDIATE FREQUENCIES (IF)

The result of converting a 27 MHz signal down to a lower frequency during reception is an "Intermediate Frequency" or "IF". This stage is often the only IF, as shown in Figure 2-A. However when a double conversion occurs, the result is two IFs. These are called the "first" or "high" IF and the "second" or "low" IF, Figure 2-B. For CB use, these two IF frequencies are almost universally 10.695 MHz, and 455 KHz. This is partly because there was already a lot of existing electronic equipment using these IFs long before CB radios came along. (Eg, AM and FM broadcast receivers, portables, shortwave receivers, scanners, auto radios, etc.) Thus the needed parts were already available to manufacturers, proven reliable, and cheap. Another reason is because a very clever use of the PLL circuit, which is almost always based upon a 10.240 MHz Master Oscillator, can be made to provide these IF "injection" signals. When the injection signal is above the CB signal, it's called "high-side" injection, and "low-side" injection is when it's below the 27 MHz CB signal. Older PLLs used both methods but the very newest chips use low-side injection for reasons you'll see later.

#### FIGURE 2. FREQUENCY CONVERSION PROCESS

Several very popular CB chassis types use only a single IF of 7.8 MHz. (Eg, Cobra 140/142GTL or Superstar 360 with MB8719 PLL, Cobra 138/139XLR or President "Adams" with 858 PLL.) In doing this, receiver performance was cheapened and selectivity worsened. The fact that these particular chassis are still extremely popular today is because they are very easy to modify, not because of their great receiver performance! A deluxe version of the MB8719 chassis (Eg, Cobra 148/2000GTL, new President "Madison" and "Grant") offers not only an easy modification, but here the manufacturers took the trouble of using dual conversion on AM with a standard 455 KHz IF. They also charged you more for this feature. Separate filters could be used for each mode to increase selectivity, because an SSB signal only requires about half the bandwidth of AM or FM. Where in the first example a compromised IF filter bandwidth is used which is basically too wide for SSB and too narrow for AM/FM, in the "deluxe" chassis you get excellent selectivity in every mode. The use of separate SSB and AM/FM IFs is also found in all American and European versions of rigs using the very popular PLL02A PLL chip. This short background on design trade-offs will help your understanding of PLL mixing circuits to be described later.

#### SSB MIXING

Some unique problems occur with PLL or crystal rigs in the SSB mode. With AM and FM rigs, all we need to do is to generate (or receive) a carrier signal and then modulate (or demodulate) it. However for SSB, the only signal that exists is on a radio frequency but is changing at an audio rate, above and below the suppressed carrier. The voice intelligence is contained only in the upper (USB) or lower (LSB) "sidebands". For voice communications, these sidebands are limited to about 3 KHz above and below the main carrier frequency. (The limiting occurs by filtering in the mike amplifiers and the sharp IF crystal filter.) For example on U.S. Channel 1, 26.965 MHz, the USB signal would extend up as high as  $26.965\,\mathrm{MHz}$  +  $.003\,\mathrm{MHz}$  =  $26.968\,\mathrm{MHz}$ . The LSB signal would extend down as low as 26.965 MHz - .003 MHz = 26.962 MHz. (3 KHz = .003 MHz for those of you who didn't realize I converted to make the math easier.) The PLL circuits must therefore be able to offset themselves slightly, mixing with the other required signals during SSB reception or transmission. In addition, the carrier oscillator which provides the carrier for all modes (AM, FM, SSB) must also be detuned or offset slightly for SSB, (+) or (—) as appropriate. In this way the mixing process will produce the correct frequency for on-channel operation. The SSB offsets are done very easily by switching in a small bit of capacitance or inductance whenever you change the mode switch. (This same detuning idea is used on AM or FM rigs that have a front panel DELTA TUNE control.)

A very sharp IF crystal filter is needed for SSB which will only pass one of the two sidebands. This filter is usually a large rectangular metal can on the main PC board. The newer Uniden chassis has its filter actually built on a small PC board which sticks up vertically from the main PC board. These filters are *very* expensive because they use up to 8 quartz crystals to get their sharp selectivity. Since you would need two of these very expensive filters, one for USB and one for LSB, it's much cheaper to offset the PLL and carrier oscillators through the appropriate switching rather than use two filters for two slightly different IF frequencies. In other words, a *constant* IF is maintained during SSB use. The cost of a few resistors, capacitors, transistors, or even a second crystal oscillator is only a fraction of the cost of that second IF filter.

The offset process will be very obvious as you study the SSB block diagrams in Section III, and is also the reason you will see slightly different VCO frequencies shown in the rig's service manual charts. The offset detuning in SSB is still not quite good enough during reception, which is why SSB rigs must also have a front panel control called a "Clarifier", "Fine-Tune", "Voice Lock", etc. The more common CB term is "slider" or "KC shifter". This circuit is nothing more than an additional tuning inductance or capacitance wired in parallel with the main USB/LSB offset mixers. Think of it as an extra-fine-tune adjustment to the offset mixing process. The range of most sliders is factory-limited to about ± 1 KHz from channel center, and only works in the Receive mode. A very common modification is to "strap over" the slider so that it will also shift during the Transmit mode. It's not only very easy to do this, but also to increase the slide range up to about  $\pm 5$ KHz. (Detailed methods for doing this are described in our book, THE "SCREWDRIVER EXPERT'S" GUIDE.) Later you'll see exactly how the offset SSB mixers and clarifiers are connected in the PLL circuit.

#### THE "ODD" BRITISH CHANNELS

Many people have asked how the unusual U.K. CB channels affect PLL operation. The channels are 27.60125 MHz at Channel 1 up to 27.99125 MHz at Channel 40, with standard 10 KHz channel spacings. The answer is that the PLL itself has practically nothing to do with it! Surprised? A big fuss was made over the belief that when CB was recently legalized in Britain, the rigs would need special PLL chips. As it happens, most rigs do have special chips but not because of the unusual frequency assignment. It would have been just as easy to use existing chips. The fact that U.K. Channel 1 is 27.60125 MHz rather than a nice round number like 27.600 MHz is easily accomplished in the offset mixing process like that just described for SSB. This process is external to the PLL chip itself. A PLL is only intended to synthesize or

generate the channel *spacings*. The additional 1.25 KHz above 27.600 MHz (or 3.5 KHz *below* 27.605 MHz if you prefer) can be set by tuning coils in the rig at the factory, or by you with an external slider control. The new U.K. chips are identical to most of the latest American chips, literally pin-for-pin the same functions. The only difference is in the chip's "N-Code" set and the 1.25 KHz offset detuning of all transceiver stages shown in Figure 3. (N-Codes will be explained in great detail later.)

#### THE PLL FOR FM USE

The use of FM over AM or SSB is legally required in many countries. Ironically it's now becoming popular in the U.S. where it is officially illegal! Most of the very popular European rigs (Eg, Ham International, Major, Superstar) are simply the basic American chassis with extra channels and FM already wired in. The most popular current American manufacturers such as Cobra, Midland, President, and Colt have jumped at the chance to expand their markets by adding the same circuits to their American chassis and exporting them abroad. The PLL circuits of all these rigs are basically identical and the differences will be pointed out as we progress. First though, let's see how the PLL is used for FM operation.

During reception, the FM/PLL circuit is identical to any other AM or AM/SSB rig. The PLL is only needed to provide the channel spacing and selection, and the IF injection frequencies. To receive FM, a special FM detector circuit is switched in. This circuit is typically a single IC and a few external parts having nothing at all to do with the PLL. FM, AM, and SSB are all detected *after* the PLL has done its job on the RF carrier by IF mixing. (Special PLL chips such as the NE561 are actually used as FM detectors, but that's another subject entirely!)

FM transmission is where our PLL's flexibility is used. The PLL circuit uses a very sensitive stage called a "Voltage-Controlled Oscillator" or "VCO". The smallest change in the DC control voltage to a VCO circuit will make it change its frequency. For the moment, just think of FM transmission as a means of adding this small voltage fluctuation to the VCO. The fluctuating voltage is taken from the mike amplifier circuit and is *very* small compared to the amount of voltage that would shift the rig to a completely different channel.

In addition this FM voltage is changing at an audio rate, literally rising and falling up to 3,000 times per second. (Assuming the audio is limited to the 3 KHz maximum typical of two-way radio systems.) The

FIGURE 3. OFFSET TUNING FOR NON-STANDARD U.K. RIGS, SSB, etc.

Tuning circuits offset VCO frequencies by proper amount to produce desired frequencies, external to the PLL chip itself.

word "modulation" simply means changing something in proportion to something else. Instead of changing the RF carrier power in proportion to the mike audio as in AM/SSB, the carrier frequency is being changed in proportion to the mike audio. With FM transmission we are simply taking advantage of the fact that the PLL's VCO is so sensitive.

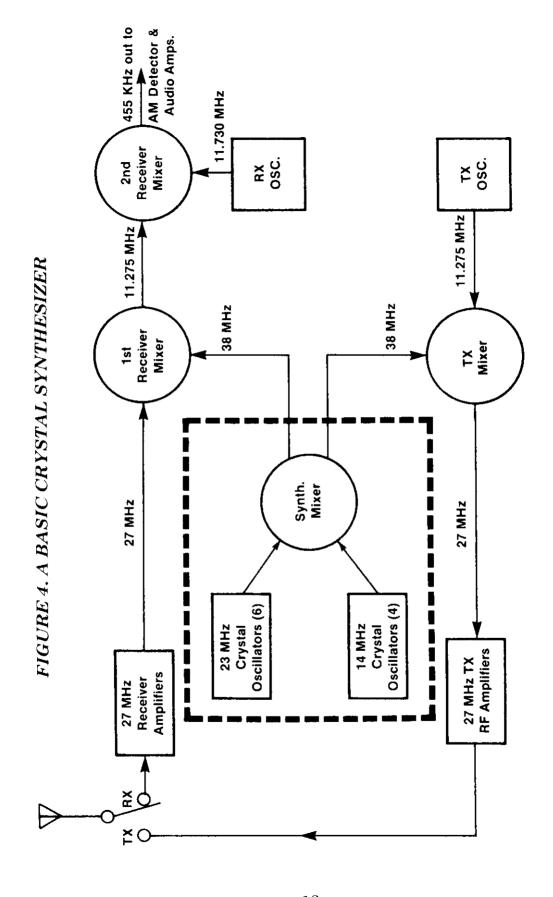

#### A BASIC CRYSTAL SYNTHESIZER

To better understand what a PLL does, let's first compare it to the older crystal-synthesized method of signal generation. This is easy to do if you think of the entire crystal or PLL synthesizer as a "black box" within a larger black box, namely the whole radio. Figure 4 illustrates a very common AM crystal synthesizer in block diagram form. It uses 12 crystals to synthesize 23 channels. View the synthesizer within the dotted lines as a single box rather than the three smaller blocks which comprise it. In the next step we'll just replace the internal workings of the big box with a PLL instead.

In this arrangement there are two banks of crystals operating in the 14 MHz and 23 MHz range. Changing the channel simply combines a different pair of crystals together. When each crystal bank's oscillator is combined in a mixer and passed through tuned circuits, the sum frequency of approximately 38 MHz is chosen. This 38 MHz signal is sent to both a Transmit Mixer stage, and the First Receiver Mixer stage. In the Receiver Mixer, the incoming 27 MHz signal is combined with the 38 MHz signal from the synthesizer. The difference frequency in the 11 MHz range (38 MHz — 27 MHz = 11 MHz) is chosen this time by tuned circuits and becomes the first receiver IF. This 11 MHz IF is then passed along to a second mixer where it's combined with the output from a separate 11.730 MHz crystal oscillator. The difference frequency is chosen again; this difference is the standard 455 KHz second IF which is then detected and amplified in the audio chain.

The transmit mixing is much simpler. The 38 MHz signal sent to the Transmit Mixer from the synthesizer is mixed with a separate 11.275 MHz Transmit Oscillator. The difference frequency of 27 MHz is chosen, passed through tuned circuits, amplified and modulated.

Here's a specific example: For U.S. Channel 1,  $26.965\,\mathrm{MHz}$ , the Channel Selector switch will connect crystals of  $23.290\,\mathrm{MHz}$  and  $14.950\,\mathrm{MHz}$ . These two signals mix to produce a signal of  $23.290\,\mathrm{MHz} + 14.950\,\mathrm{MHz} = 38.240\,\mathrm{MHz}$ . In the Transmit Mixer, this  $38.240\,\mathrm{MHz}$  signal will mix

with the 11.275 MHz Transmit Oscillator, producing a difference of 26.965 MHz which is the correct on-channel frequency. (38.240 MHz –11.275 MHz = 26.965 MHz.) Notice that the transmitted signal is only converted once in frequency, and this will also be true for PLL circuits. However the receiver, being AM, uses dual-conversion for best performance. So its signal is converted down once more. The incoming signal of 26.965 MHz first mixes with the 38.240 MHz synthesizer signal, the difference is chosen, and the result is the first IF of 11.275 MHz. (38.240 MHz — 26.965 MHz = 11.275 MHz.) When this first IF is then mixed with the separate 11.730 MHz Receiver Oscillator, the result is 455 KHz. (11.730 MHz — 11.275 MHz = 455 KHz.)

Earlier I mentioned that PLLs use IF frequencies that are usually 10.695 MHz and 455 KHz partly because a lot of existing tuning coils were available. In this example the first IF is obviously 11.275 MHz but in fact the tuning coils are still the same as they would have been for 10.695 MHz; these coils can cover a wide frequency range. Remember this when examining specific PLL circuits because you may find that the math for the IFs doesn't compute exactly; if the IF appears to be slightly different from that calculated or shown on the circuit diagram, it's because these tuning coils are often detuned slightly to pass the correct frequency.

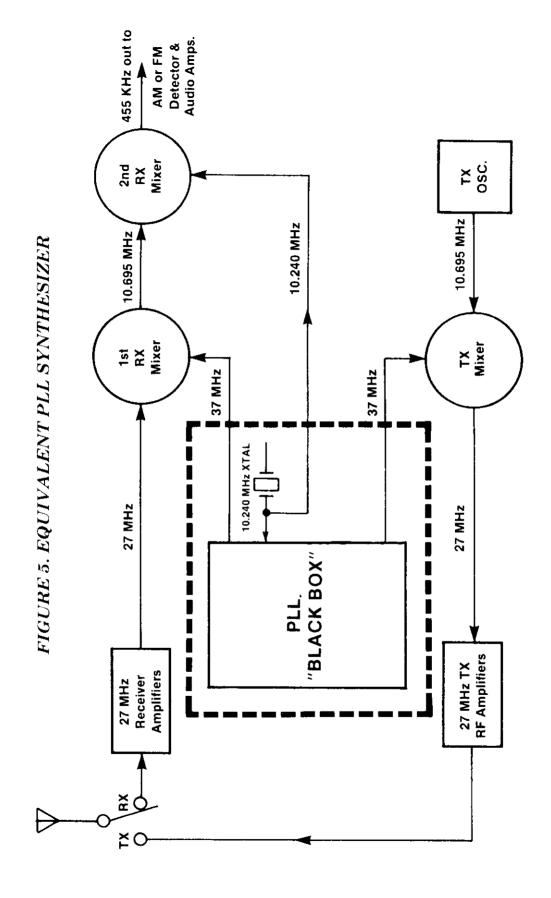

#### **EQUIVALENT PLL SYNTHESIZER**

Now let's substitute a new "box" for that of the crystal synthesizer. The internal workings of the box itself will be saved for later. For the moment, just picture it as a total unit and you'll understand it more easily. Figure 5 shows a circuit which is almost identical to the crystal synthesizer of Figure 4. All the mixers and conversions are the same. The PLL synthesizer simply produces an exact signal in the 37 MHz range, depending upon the setting of the Channel Selector switch. This signal goes off in two directions again, to the Transmit Mixer and First Receiver Mixer.

During Transmit, this 37 MHz PLL output is mixed with a signal coming from a separate 10.695 MHz crystal oscillator circuit. The mixture passes through tuned circuits which select the difference frequency in the 27 MHz range and is the actual on-channel frequency, similar to the previous example.

During Receive, the 37 MHz signal from the PLL mixes with the

incoming 27 MHz signal to produce the first or high IF, which in this case is 10.695 MHz. This signal then passes to the Second Receiver Mixer. In this stage, a very clever extra use is made of the PLL box. It so happens that almost all PLLs require a "reference oscillator" circuit of 10.240 MHz to operate. By borrowing a bit of that 10.240 MHz energy and sending it up to the Second Receiver Mixer, guess what happens? Here's the math: 10.695 MHz — 10.240 MHz = 455 KHz! Once again, we've managed to make a dual-conversion receiver, and with standard tuning circuits.

Notice a small but subtle difference in my labeling on the right-hand side of Figures 4 and 5. In the crystal synthesizer, the second receiver mixer output says "455 KHz to AM Detector" while in the PLL synthesizer it says, "455 KHz to AM or FM Detector. Why not FM for the crystal version? Disregard the fact that FM CB is not legal in the U.S. and that CB had not yet been discovered in the rest of the world where it often is legal. The reason is purely technical. It's very difficult to frequency-modulate a crystal oscillator for 27 MHz use; the crystals can't be "pulled" far enough away from their cut frequencies for proper FM deviation to occur. Commercial two-way FM radios that operate in the VHF or UHF bands can be easily crystal-controlled because the crystal is multiplied up many times in frequency for final operation. When such a signal is multiplied up, any change in the controlling crystal frequency will also be multiplied by the same amount. With the PLL, we use a VCO circuit that's very sensitive, and can easily generate FM where a crystal-synthesized rig could not.

#### **ELEMENTS OF THE PLL SYSTEM**

Time now to look inside the mysterious "black box"; I can't avoid it any longer! If you're with me so far you'll have little trouble. The description will be very basic here, getting more specific as we progress.

Trying to describe PLL operation is a little like the situation of giving somebody a very small gift wrapped up in a very large box. There's a box within a box within a box, all covered with wrapping paper. So far we've only looked at the wrapping; time to see what's inside! Part of the problem lies in the name, Phase-Locked-Loop. There's no real beginning to a loop or circle, so it's possible to jump in anywhere. Once you understand what each main PLL element does, you can pick the starting point that you prefer.

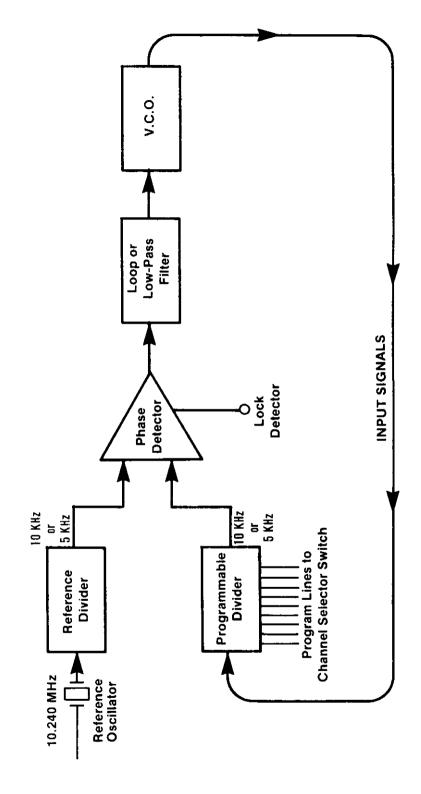

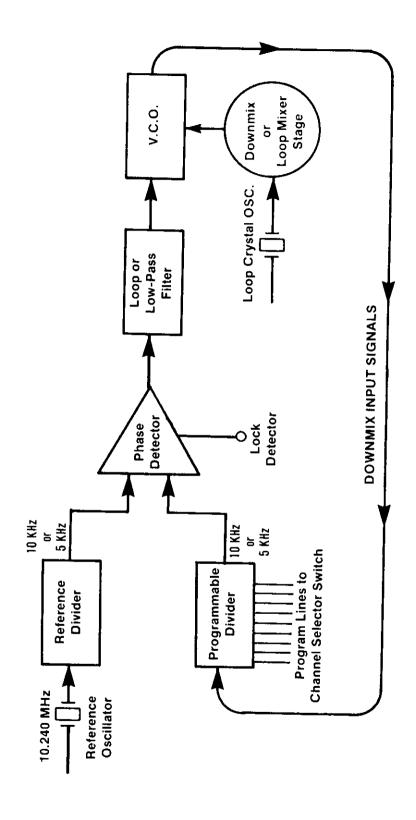

Figure 6 shows the basic elements of any PLL system. Arrows show the direction of signal flow. It's obvious that the signal goes around in one

FIGURE 6. BASIC ELEMENTS OF ANY PLL SYSTEM

big circle or loop. The order I've chosen to describe each element is one which I think is the easiest to understand. The major building blocks are:

- 1. Reference Oscillator & Divider;

- 2. Programmable Divider;

- 3. Phase Detector;

- 4. Loop or Low-Pass Filter;

- 5. Voltage-Controlled Oscillator (VCO)

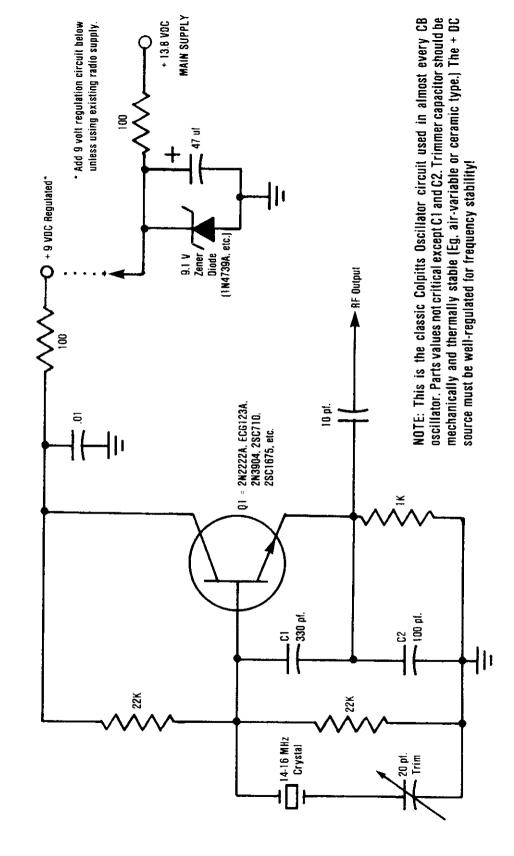

#### REFERENCE OSCILLATOR & DIVIDER

This circuit connects to the outside world through an ordinary crystal oscillator. The very newest chips have internal oscillators where all that's needed is the crystal itself and a few capacitors. However the majority of chips in current use still need an actual transistor oscillator circuit with the crystal. This oscillator operates almost universally at a frequency of 10.240 MHz. (A few very old designs used other crystals such as 5.12 MHz or 10 MHz.) The reason is because with "digital" electronic circuits, it's very easy to divide a signal of 10.240 MHz by the number "1,024". If this is done, the result is an output from the divider of 10 KHz, (10.240 MHz  $\div$  1,024 = 10 KHz) which just happens to be the required channel spacing for most of the world's CB services. Sometimes a few channels skip around by 20 or 30 KHz but this is accounted for in the next section, the Programmable Divider.

I said digital techniques were used with PLLs. This word "digital" refers to any electronic circuit that can only recognize one of two distinct states, which are typically called "1" and "O", "HIGH" and "LOW", or "ON" and "OFF". Think of a digital device as simply a switch, such as the ON/OFF switch on the rig. The electronic opposite of digital is "analog", which is a circuit that can change its values continuously from each possible extreme and theoretically has thousands of possible values. The VOLUME control is an analog device.

Many of the most recent chips actually use the 10.240 MHz reference signal to divide down by 2,048, giving a divider output of 5 KHz rather than 10 KHz. And some chips can select either division ratio. The 5 KHz steps make certain PLL functions easier to accomplish, as we'll see later.

The purpose of the Reference Divider is to provide a very stable comparison signal against which all other signals will be synthesized. It's obvious that if the 10.240 MHz signal is not exactly on frequency, none of the other PLL signals will be either. So all PLL circuits have some way to trim their outputs to the correct frequency. The majority of PLLs use a small value trimming capacitor or coil in the reference crystal circuit, although a few PLLs make the adjustments later in the loop.

#### PROGRAMMABLE DIVIDER

This is really the heart of the PLL synthesizer, and a common source of frequency modifications and expansions in most older chips. By connection to the outside world at the Channel Selector switch, a command is made to divide down whatever signal it's receiving from the VCO by a precise number. This number is generated using digital techniques and is called an "N-Code", "÷ N", or "Divide-By-N" number. The N-Code is a number based upon the digital or "binary" number system rather than the common decimal system used by people. The word "binary" refers to a pair of two things and it was already pointed out that a digital circuit can only recognize two states.

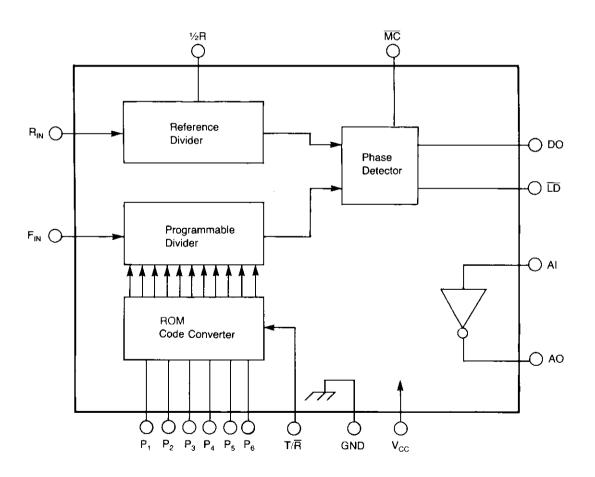

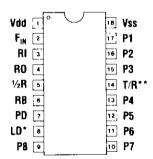

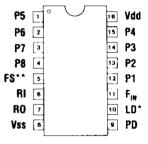

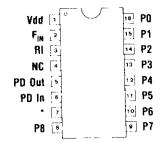

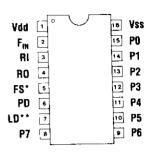

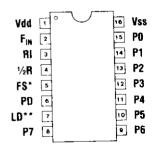

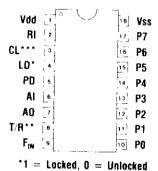

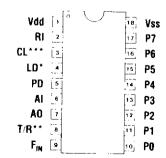

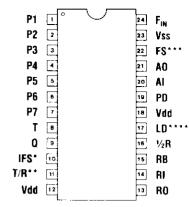

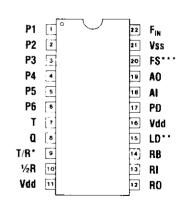

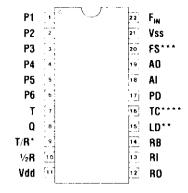

Each position of the Channel Selector switch changes the N-Code slightly by connecting either a positive DC voltage ("1") or ground ("O") to the appropriate IC pins on the PLL's Programmable Divider circuit. There are typically 6 to 10 pins on the chip devoted to the programming function. On the cover of this book is a chip's Block Diagram showing "P<sub>1</sub>" to "P<sub>6</sub>"; the "P" stands for "Program". The programming pins are called "bits" and the total number of programming pins or bits has a direct relation to the number of possible channels which can be synthesized. Many times a special type of N-Code called "Binary-Coded-Decimal" or "BCD" is used instead of the ordinary binary code. This is partly because there's a lot of electronic support hardware around using BCD inputs, such as keyboard controls and LED number displays. It's also because when used with the very newest chips, BCD programming helps make modifications almost impossible.

#### PHASE DETECTOR

This circuit is the decision-maker in the PLL. It receives two signals from both the Reference Divider and Programmable Divider and

compares them, looking for an exact match in the divided-down frequencies. The Reference Divider will usually be exactly 10 KHz or 5 KHz. (10.240 MHz  $\div$  1,024 or 2,048.) However the input from the Programmable Divider may not necessarily be these exact frequencies, in which case an error exists. The Phase Detector is intended to sense this error and do something about it. When inputs to the Phase Detector are not matched, the loop is said to be "unlocked" or "searching." The Phase Detector must bring the loop into lock by an appropriate output command to the VCO. This command is in the form of a very small DC correction voltage, (+) or (—) as required. Most phase detectors have a second output called a "Lock Detector". If a great error exists between the compared signals that can't be corrected in the normal way, the Lock Detector switches to its opposite logic state. For example, if the Lock Detector is normally at a logic "1" or high DC voltage, the out-oflock condition will cause it to switch over to the "O" or grounded state. This change is sensed by an external switching circuit that's usually wired to turn off the transmitter (and sometimes even the receiver), preventing off-frequency or unstable operation. How far the loop can vary within its normal lock-up frequencies is called its "capture range."

#### LOOP OR LOW-PASS FILTER

This circuit immediately follows the Phase Detector, and is designed to smooth out the digital waveform entering the VCO circuit. Because the Phase Detector is sampling and comparing inputs at a digital rate, literally millions of times per second, there will always be highintensity "spikes" coming out of it. It's impossible for any electrical or mechanical device to switch on and off instantaneously; you can't go from zero to some higher value just like that. (No doubt you've seen your house lamps dim slightly when a large motor like an air-conditioning compressor suddenly switched on; it took time for things to equalize.) If these spikes were allowed to pass on to the VCO, they could cause the oscillator's frequency to "jitter" around unstably. The spikes are of a higher frequency than the normal digital pulse, and that's why this element is often called a Low Pass Filter. It stops high frequencies from passing through it. This is exactly the same idea as the Low Pass filter used on the back of a rig which prevents high frequency harmonics from causing TVI.

The Loop Filter may be a circuit as simple as a capacitor/resistor combination at the output of the Phase Detector, or it can take the form of an actual "active filter" inside the chip itself. The active filter is now more common as engineers figured out how to cram more and more functions into the chip structure itself. This simplifies design (and cost!)

by reducing the number of external circuit parts needed. The Loop Filter is sometimes called a "Charge Pump" because its input capacitor charges up to help keep the output waveform very pure.

#### **VOLTAGE-CONTROLLED OSCILLATOR (VCO)**

The VCO is a very interesting circuit that has many uses in electronics besides CB radios, such as the Automatic Fine Tuning (AFT) in a TV or stereo receiver. The VCO is an oscillator whose frequency is determined not by the usual coils, capacitors, or quartz crystals, but rather by a special device called a "varactor" or "varicap" diode. It's extremely sensitive to the slightest change in DC voltage applied across it. As the voltage increases, the diode's internal capacitance decreases, changing the VCO's frequency. Increasing the voltage can make the frequency go up or down depending upon how the varactor is wired in the circuit, and both methods have been used in CB VCOs. The output of the Phase Detector looks exactly like a "staircase" of DC voltage levels when going through the range of channels, and the tiniest step up or down will shift the VCO to the next channel. If you measured this voltage at the chip with a voltmeter, you'd find a change as small as .05 volts DC will shift an entire 10 KHz over to the next channel!

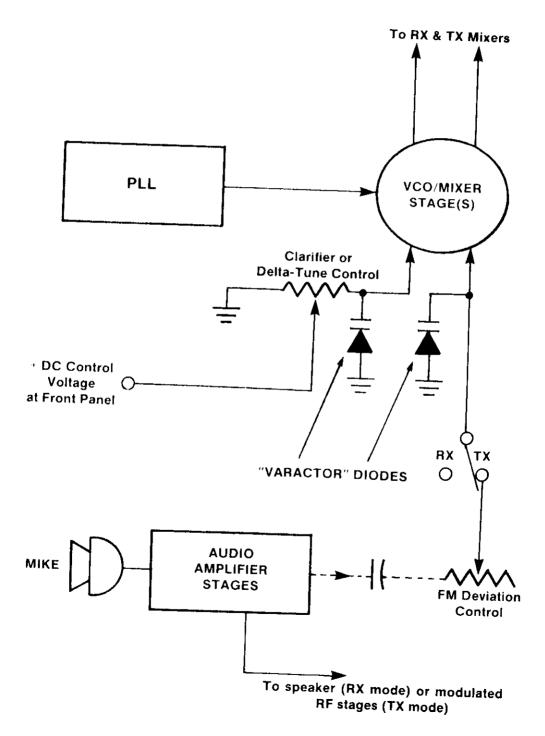

Because the VCO is so sensitive to voltage changes, we can make very good use of this fact for FM transmission, SSB slider circuits, and Delta-Tune controls on AM/FM rigs. If you study the schematic diagram of such a rig, you'll always find an extra varactor diode somewhere in addition to the one used in the VCO itself. Figure 7 shows this general idea. For the SSB slider or Delta Tune, a control on the rig's front panel is used to change a DC voltage across a varactor diode; this in turn changes the varactor's capacitance slightly and therefore the frequency too. (A much more detailed explanation of slider circuits and specific popular chassis modifications can be found in THE "SCREW-DRIVER EXPERT'S" GUIDE.)

For FM transmission, some of the audio from the mike amplifier circuit is sampled off to be used as a control voltage. This voltage, which remember is changing at an *audio* rate, is applied to another varactor in the VCO or Mixer stage at a sensitive place. The result is FM rather than AM or SSB.

Continuing around the loop, you'll see that the VCO's output is fed right back into the Programmable Divider and then to the Phase Detector. The Phase Detector then decides whether or not a 10 KHz (5 KHz) match

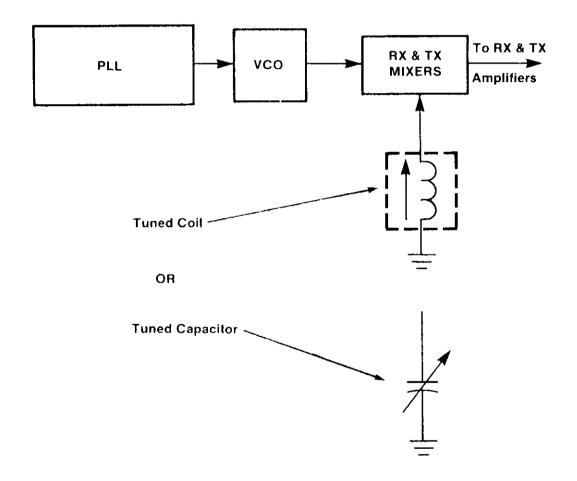

### FIGURE 7. USING THE SENSITIVE VCO STAGE TO PRODUCE SSB/DELTA-TUNE OFFSETS OR FM

exists between the Reference Divider and the Programmable Divider. If so, the loop is locked on frequency. If not, the Phase Detector senses this difference and outputs a DC correction voltage to the VCO. This drives the VCO up or down slightly in frequency until an exact match is found and the loop locks. This entire PLL process can be compared to a self-correcting mechanical servo system for those of you who are mechanically inclined. Although it may take many comparison cycles before an exact match is found, the entire process happens in the wink of an eye!

You really begin to appreciate the accuracy of any PLL system when you can compare it to the older crystal-synthesized rigs. For example, using an 8-digit Frequency Counter, I compared the carrier frequency accuracy of both types. Where the crystal rig might indicate say, 26.965316 MHz on Channel 1 and 26.975124 MHz on Channel 2, the PLL rig will typically show something like 26.965004 MHz on Channel 1, 26.975004 MHz on Channel 2, and 27.405004 MHz on Channel 40. In other words, the PLL is accurate all the way down to the last decimal place!

We've now come full circle around the loop and hopefully you're still there. It's now necessary to complicate things a bit more because certain other PLL circuit functions must be explained to complete your basic understanding.

#### THE LOOP MIXER OR DOWN CONVERTER

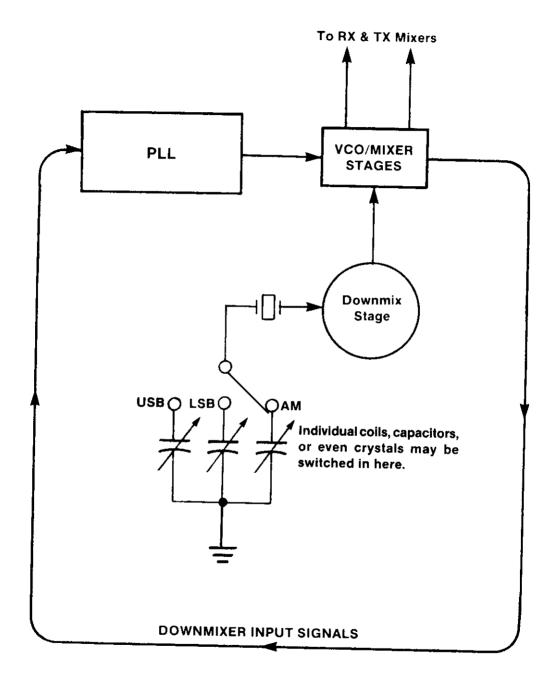

The need for Intermediate Frequencies and SSB offset mixing has been explained. You've also seen how the very sensitive VCO circuit can change the carrier frequency, slide an SSB clarifier, and generate FM transmission. However there's still one more basic mixing process required in the majority of rigs that use the older chip technology. While this process complicates the circuitry, it also makes modifications a lot easier!

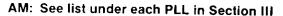

The extra mixing circuit is called the "Loop Mixer", "Down Mixer", or "Down Converter". Figure 8 shows its addition to the basic PLL circuit. Notice that except for the addition of this extra mixer, the PLL circuit is identical to that of Figure 6 on Page 17. A separate crystal-controlled oscillator provides the extra mixing signal, and may be used directly or multiplied up to get it close to the VCO frequency.

FIGURE 8. A BASIC PLL SYSTEM WITH DOWNMIX STAGE ADDED

The reason many older PLLs require this extra mixing process is that they were not able to directly divide down the incoming VCO signal to the Programmable Divider. Most common VCOs run in the 16 MHz or 37 MHz range, and a frequency this high was impossible for older digital dividers to handle; they just weren't fast enough. Nowadays the newest "CMOS" PLL chips have been improved to the point where they are able to divide down a signal as fast as 20 MHz. Such chips are typically found only in AM or FM dual conversion rigs. You'll eventually learn to hate this particular technological improvement, because the Down Mixer stage was one of those perfect spots to modify the rig's frequencies by injecting a different mixer signal with another crystal.

For SSB use, the Down Mixer is again offset slightly in frequency, as seen in Figure 9. When you switch to LSB or USB, separate coils and/or capacitors are placed in the circuit whose values will detune the main loop oscillator by the correct amount. The offset circuits are typically switched in by diodes or transistors, and may have fixed values or factory-adjusted trimmers. In most rigs the varactor circuit which slides the Clarifier is also connected here. However there is one current SSB chassis (with uPD2824 chip) where the 10.240 MHz crystal connects to the Clarifier but a separate oscillator crystal is the one offset for the carrier itself. (Eg, Cobra 146GTL, President AR-144, Realistic TRC451, Sears 663.3810.)

The Loop Mixer usually takes a signal generated from some other oscillator and mixes it with the VCO signal. Tuned circuits then pass only the difference frequency on into the Programmable Divider. This difference frequency is low enough to be handled by the older type of chip dividers, and is generally in the 910 KHz to 4 MHz range.

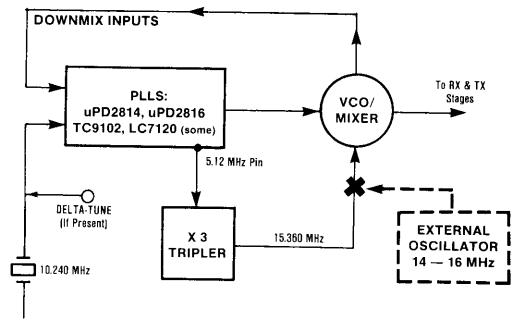

The crystal-controlled oscillator signal that's injected into the Down Mixer can come from several possible sources. The most obvious is an actual crystal oscillator using a transistor, and this is still the most common method. In many cases, this crystal frequency must be multiplied up by tuned circuits to get it close to the operating range of the VCO. The most common multiplication is by a tuned coil designed to double or triple the crystal frequency, although higher multiplications have been observed in some rigs.

#### THE 5.12 MHz LOOP MIXING OUTPUT

In many newer chips, there's a provision right on the chip itself for a signal that can be used for loop down-mixing. This signal is typically

NOTE: The Carrier Oscillator stage is normally offset also in a similiar way. This maintains a single IF frequency for all modes and thus only a single IF filter is required.

half the 10.240 MHz Reference Oscillator frequency, or 5.12 MHz. The 5.12 MHz signal comes off a pin right on the IC chip; it's already been amplified and buffered internally. The 5.12 MHz signal is normally tripled to 15.360 MHz (5.12 MHz x 3) by a tuned coil, which places it very close to a VCO running in the 16-17 MHz range. In a few Motorola rigs using the TC9105 chip, the VCO is running in the 37 MHz range, so the 5.12 MHz is multiplied up by 7 times to get it near this frequency. And in another very common arrangement, the 10.240 MHz master oscillator itself can be doubled. Borrowing this 10.240 MHz energy is a simple way to provide not only receiver IF injection as we saw earlier, but can also be used to run the loop mixer itself.

#### **CURRENT TECHNICAL TRENDS**

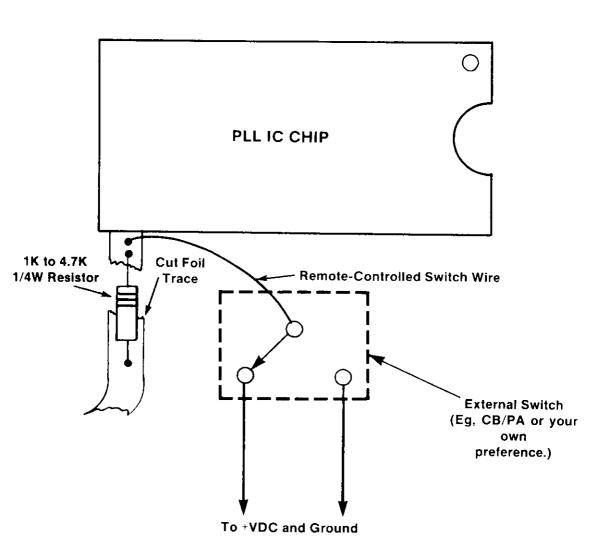

Loop mixing is one easy place for frequency modifications. Unfortunately the newest chips (Eg, LC7131, LC7136, TC9109, TC9119) which are used for dual-conversion AM or FM rigs have no loop mixing because they are capable of direct VCO division in their Programmable Dividers. In addition they use special programming tricks to further prevent modifications. If you own a rig with one of these chips, you're out of luck at the moment. There are however still millions of rigs out there using loop mixers. Many are obsolete now but the most notable exceptions are the PLL02A, MB8719, and uPD858 chassis, which are the most popular rigs in worldwide use, for obvious reasons! The AM versions of these rigs have generally disappeared because the newer chips are more foolproof. But the SSB versions are very common and still being marketed almost everywhere. That's because SSB usually requires loop mixing at this point in PLL technology, and details of common modifications can be found later in this book.

#### SPECIAL CHIP FUNCTIONS

There are several more options which may be found on PLL chips. Most deal with resistance to illegal modifications, ease of circuit design, and operator convenience features. I'll briefly summarize some of these here because you'll need to understand them whenever you're studying the pin diagram of a particular chip.

#### THE TRANSMIT/RECEIVE (T/R) SHIFT

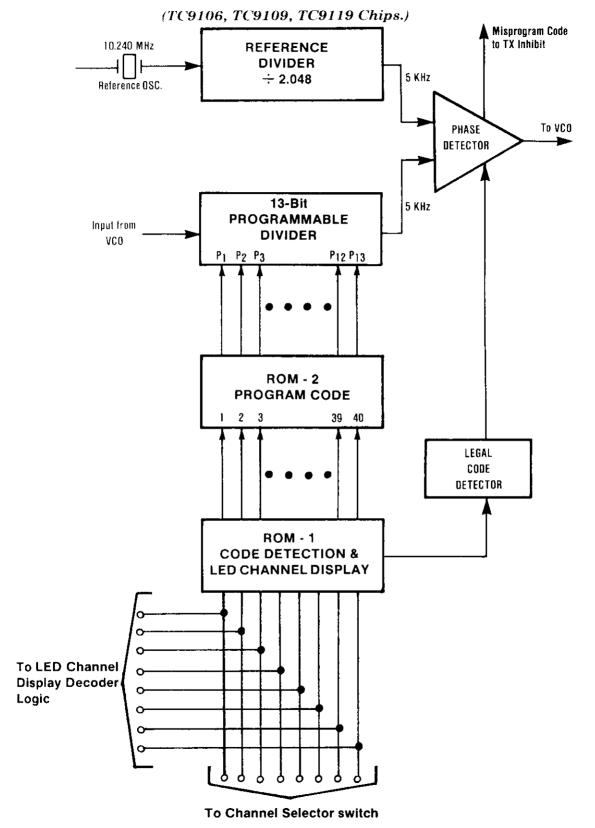

This is a function found only in the very latest generation of chips

designed mostly for AM or FM with dual-conversion receivers. Examples are the LC7120, LC7130/31, LC7136/37, TC9106, TC9109, TC9119, uPD2814, and uPD2816. A special IC pin shifts the N-Code to the Programmable Divider when that pin goes to its opposite logic state.

For example, the chip may have one set of N-Codes when the T/R pin is grounded ("O") and a different set of N-Codes when the T/R pin is high with +DC voltage applied ("1"). You'll find the chips with this feature in any rig having only a single 10.240 MHz Reference Oscillator crystal.

Because there is no other signal present in the loop that can be used for mixing, receiver IF injection, etc., it's necessary for the chip itself to generate the 455 KHz shift used for the receiver's second IF stage. The T/R pin is connected through transistor switching circuits to the mike and senses the T/R change. When this change happens, the output of the Programmable Divider entering the Phase Detector is of course no longer matching the Reference Divider's output. The Phase Detector then outputs its correction voltage to the VCO, driving it up or down to lock the loop. Generally the VCO is driven 455 KHz higher in the Transmit mode.

Chips with the T/R shift are rarely used with multimode rigs having SSB, because SSB doesn't require the second 455 KHz receiver IF conversion. One exception at the moment is the U.S. versions of the Midland 6001/7001. They use the uPD2816 chip, which has a T/R pin, but the pin is not connected; instead a separate crystal downmixer oscillator is used, which makes modification easy again. So it's possible, depending upon how the chip is used, to modify rigs that are generally non-modifiable. (Later versions of the 6001/7001 use the uPD2824, which is pin-for-pin identical to the uPD2816 minus the T/R pin function.)

The T/R families of chips are among those first mentioned using an internal 5 KHz Reference Divider output signal rather than 10 KHz. The standard 10.240 MHz crystal is used, but this time it's divided down by 2,048. (10.240 MHz  $\div$  2,048 = 5 KHz.) This is necessary because it's easy to get the 455 KHz shift; by increasing the N-Code 91 counts from the Receive N-Codes, the result is 91 × 5 KHz = 455 KHz. Some chips shift 5 KHz/2.5 KHz for T/R purposes. (Eg, PLL08A, PLL03A, TC9109.)

I've observed two other variations of the T/R shift idea. In the U.S. rigs with the TC9109 chip, the N-code shifts up by 2,139 counts in the Transmit mode while at the same time the Reference Divider shifts from 5 KHz steps to 2.5 KHz steps. This drives the VCO down from the 16 MHz range used in the Receive mode to the 13 MHz range, where it's doubled to produce the direct on-channel frequency. In the LC7136/37 U.K. rigs, the Reference Divider never changes its 5 KHz steps, but instead simply shifts down by enough counts to drive the VCO from its 16 Mhz Receive range to the 13 MHz range where it's then doubled in the same way to produce the direct on-channel 27 MHz frequency. Both designs use an IC mixer where the various VCO outputs can either be peaked (16 MHz Receive mode) or doubled (27 MHz Transmit mode) by tuned coils. The PLL03A (now obsolete) worked on this same idea but was way ahead of its time; when people discovered the rig couldn't be modified, sales of that chassis disappeared. The chip appeared long before the FCC made manufacturers use such advanced ideas!

#### MISPROGRAM CODE (MC) PIN

Many of the newer chips have special N-Code protection to prevent illegal modifications. If you try to force an illegal program code on the program pins with non-acceptable voltages and grounds, this pin function is activated. It's very similar to the Lock Detector in that it can be used to turn off the transmitter unless a legal program code exists. So once again, some of the extra "features" in the newer PLLs are for the benefit of the manufacturer and the licensing government, not for you!

#### FREQUENCY SELECT (FS) PIN

This pin, available in some older chips, allows selection of 10 KHz or 5 KHz Reference Divider steps. The division is chosen by the appropriate "1" or "O" on this pin. Don't confuse this function with the need for the 5 Khz division used with the T/R shift; it's not for the same purpose. The feature when used in the new ROM chips allows designers to synthesize frequencies in 5 KHz offsets for SSB use in addition to AM/FM use. Remember, the earlier chips were applied to CB synthesizers and many other kinds of equipment such as VHF marine radios, aircraft radios, and signal generators. It was only when people went wild with CB modifications that manufacturers were forced to make special "dedicated" ICs for CB synthesizers only.

Before you get all excited and think you can turn your rig into one having 5 KHz channels by changing the voltage on this pin, consider the fact that the N-Code programming must also change to produce 5 KHz steps in the Programmable Divider circuit as well. It can't be done easily! This pin for CB circuits will either be left unconnected on the printed circuit board, or connected to ground or +DC as needed to produce 10 KHz channel spacings. (NOTE: Frequency Expanders like the MICROMONITOR and MICROSCAN have their own PLL circuits which will replace the rig's PLL circuits, and that's why they can produce continuous 5 KHz steps.)

#### **AUTOMATIC CH.9/CH.19 COMMAND**

This is a special feature found only in the very latest chips, like the LC7130/31 for American rigs, LC7135 for 22-channel EEC rigs, and LC7136/37 for British rigs. By applying a +DC voltage to these two special pins, Channel 9 or Channel 19 is automatically recalled without changing the Channel Selector. You can just push a button, or the pins can be connected to a scanning circuit to stop on these channels when a signal is present. In addition they're connected internally to the MIS-PROGRAM CODE pin. If the MC pin is not used, as in some chassis variations, attempts to force an illegal program code will cause either Ch.9 or Ch.19 to be recalled instead of killing the transmitter. When these features are included in the rig model, the MC pin will be tied to the Lock Detector pin to kill the transmitter. If these features are not included in your rig model but you'd like to have them, it's a simple matter of fitting a SPDT switch between these pins and a +DC voltage source. (See Figure 12, Page 47.)

#### **SCANNING INTERFACE**

Certain chips such as the LC7120 and those just mentioned can be connected to special scanning chips to scan up and down the legal band, search for an unused channel, etc. These are useful features for some people and are often found in rigs having all controls in the mike and the main radio "guts" remotely hidden elsewhere in the car. (Eg, Realistic TRC462 "One-Hander".) The advantages and disadvantages should be obvious by now.

# **SECTION II**

# BACKGROUND FOR MODIFICATION METHODS

Now we're ready to get to the good part you've probably all been waiting for! Several ways to "trick" CB rigs into getting those high and low "funny" channels, as well as 10 Meter Ham conversions, will be explained in this section.

There are still two basic methods of changing frequencies in the majority of CBs. At this writing, the foolproof designs have not exactly flooded the market, especially for SSB use, and therefore most rigs can be modified using these tricks. These tricks are:

- Change the Programming N-Code on the PLL chip's pins;

- 2. Change the Loop Mixer signal.

It's not the purpose of this book to teach the basics of aligning transmitters and receivers, so if you're planning a large frequency conversion such as up into the 10 Meter Ham band, realignment of other circuits will also be required. A schematic circuit diagram of the rig is essential. However for adding one or two additional 40-channel segments to most rigs, the only alignment usually required is in the PLL's tuning circuits themselves. This part is left up to you to figure out with the aid of the circuit schematic or a more experienced friend.

Before getting more specific, I think it's important to describe an actual PLL circuit to make sure you understand its complete operation. Let's walk through the complete circuit, step by step.

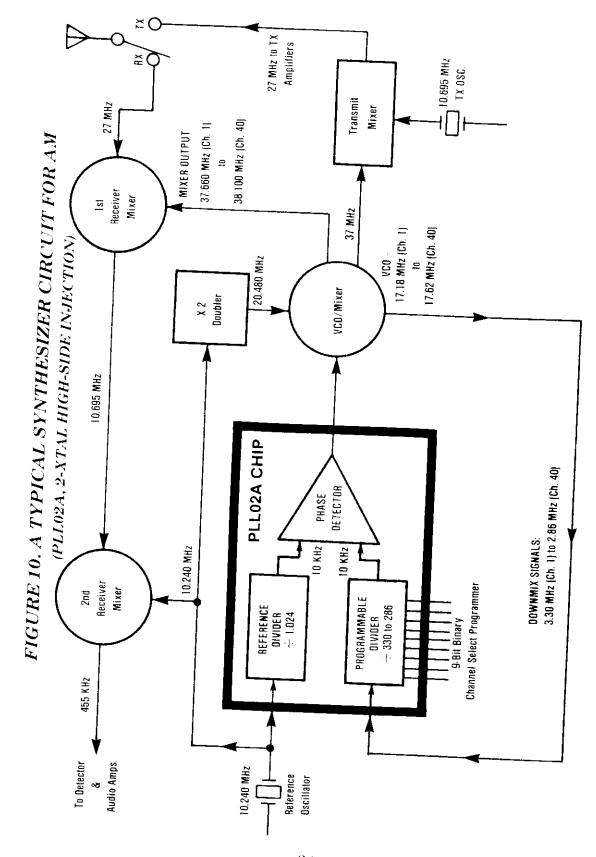

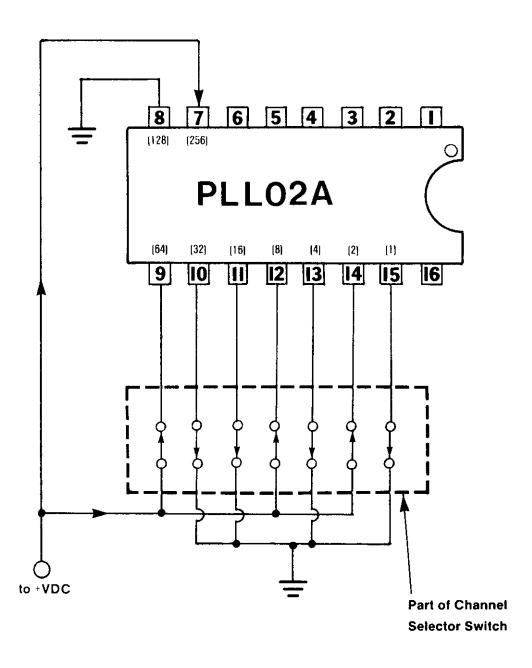

#### A TYPICAL SYNTHESIZER CIRCUIT

Refer to Figure 10 on page 34, which is the PLL circuit of perhaps the most popular AM PLL rig ever made. It's been sold under dozens of brand names and uses the ever-popular PLL02A PLL chip. The AM/SSB or AM/FM/SSB variations of this chassis are very similar when you consider the minor changes needed for SSB offsets and sliders and FMing the VCO circuit. You'll also be referring to Chart 1 on page 35, which is a breakdown of all the important operating conditions by channel number. Such a chart is normally included with the radio's service manual but certain facts not related directly to 40-channel operation are often left out. I'll be filling in the missing blanks for you.

A PLL circuit may be categorized very generally by the number of crystals it uses and by whether its VCO is running for low-side or high-side receiver IF injection. This example is actually the second generation PLL02A AM circuit; the first one used a 3-crystal loop and can be found in Section III. The newest chips use a single 10.240 MHz crystal and low-side VCO operation in the 16-17 MHz range where the VCO can be directly divided without a loop Down Mixer.

The key to synthesizing all the required frequencies is in the Programmable Divider, which is the only PLL section that you can control from the outside world at the Channel Selector switch. That switch is where the whole process begins.

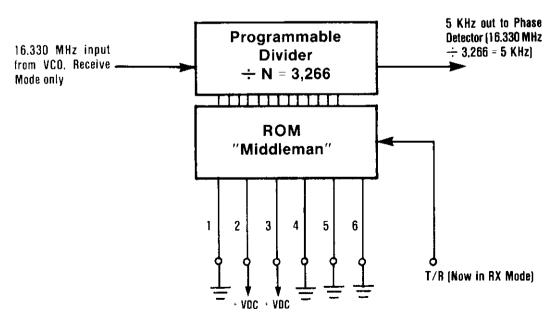

Suppose you choose U.S. Channel 1, 26.965 MHz. (This description applies to all circuits and chips.) In the Channel 1 position, the Programmable Divider receives a very specific set of instructions at its programming pins, which are directly connected to the Channel Selector. This particular instruction set, called an "N-Code", applies only to Channel 1 and is nothing more than a number which will divide down any signal appearing at the Programmable Divider input by that number

#### **BINARY PROGRAMMING**

Referring now to Chart 1, you see the N-Code for Channel 1 is the number "330" and the numbers progress down to "286" at Channel 40. The number 330 is the direct result of applying a +DC voltage of typically 4-8 volts to certain PLL program pins while grounding certain other pins at the same time. Recall that the PLL requires a digital or binary counting system rather than the common decimal system used by people.

In a binary number system, each successive programming pin or "bit" is worth exactly twice (or half) that of the pin next to it, such as 1, 2, 4, 8, 16, etc. A series of "1s" and "Os" appears in the chart for each of the 40 channels. The "1" means +DC is applied to that pin, and the "0" means that particular pin is grounded. The greater the "Power-of-2" controlled by a pin, the greater its "significance". As you'll see next the greatest Power-of-2 for this example is 256 on Pin 7. Therefore Pin 7 is called the "Most Significant Bit" (MSB) and the "Least Significant Bit" (LSB) is Pin 15, which only has a weight of 1. A chart like Chart 1 that shows the logic states ("1" or "0") of each PLL program pin for each channel is

CHART 1

Circuit Constants & Truth Chart For Sample PLL Synthesizer Described in Text

| Channel<br>No. | Channel<br>freg. (MHz) | "N" digital | VCO freq.<br>(MHz) | Rx 1st<br>IF freq.<br>(MHz)             |    |    |    | IC P | rogra | m Pins |   |     | -  |

|----------------|------------------------|-------------|--------------------|-----------------------------------------|----|----|----|------|-------|--------|---|-----|----|

| 110.           | 110q. (m112)           | 60465       | (1411.72)          | (************************************** | 15 | 14 | 13 | 12   | 11    | 10     | 9 | 8   | 7  |

| 1              | 26.965                 | 330         | 17.18              | 37.66                                   | 0  | 1  | 0  | 1    | 0     | 0      | 1 | 0   | 1  |

| 2              | 26.975                 | 329         | 17.19              | 37.67                                   | 1  | 0  | 0  | 1    | 0     | 0      | 1 | 0   | 1  |

| 3              | 26.985                 | 328         | 17.20              | 37.68                                   | 0  | 0  | 0  | 1    | 0     | 0      | 1 | 0   | 1  |

| 4              | 27.005                 | 326         | 17.22              | 37.70                                   | 0  | 1  | 1  | 0    | 0     | 0      | 1 | 0   | 1  |

| 5              | 27.015                 | 325         | 17.23              | 37.71                                   | 1  | 0  | 1  | 0    | 0     | 0      | 1 | 0   | 1  |

| 6              | 27.025                 | 324         | 17.24              | 37.72                                   | 0  | 0  | 1  | 0    | 0     | 0      | 1 | 0   | 1  |

| 7              | 27.035                 | 323         | 17.25              | 37.73                                   | 1  | 1  | 0  | 0    | 0     | 0      | 1 | 0   | 1  |

| 8              | 27.055                 | 321         | 17.27              | 37.75                                   | 1  | 0  | 0  | 0    | 0     | 0      | 1 | 0   | 1  |

| 9              | 27.065                 | 320         | 17.28              | 37.76                                   | 0  | 0  | 0  | 0    | 0     | 0      | 1 | 0   | 1  |

| 10             | 27.075                 | 319         | 17.29              | 37.77                                   | 1  | 1  | 1  | 1    | 1     | 1      | 0 | 0   | 1  |

| 11             | 27.085                 | 318         | 17.30              | 37.78                                   | 0  | 1  | 1  | 1    | 1     | 1      | 0 | 0   | 1  |

| 12             | 27.105                 | 316         | 17.32              | 37 80                                   | 0  | 0  | 1  | 1    | 1     | 1      | 0 | 0   | 1  |

| 13             | 27.115                 | 315         | 17.33              | 37.81                                   | 1  | 1  | 0  | 1    | 1     | 1      | 0 | 0   | 1  |

| 14             | 27.125                 | 314         | 17.34              | 37.82                                   | 0  | 1  | 0  | 1    | 1     | 1      | 0 | 0   | 1  |

| 15             | 27.135                 | 313         | 17.35              | 37.83                                   | 1  | 0  | 0  | 1    | 1     | 1      | 0 | . 0 | 1  |

| 16             | 27.155                 | 311         | 17.37              | 37.85                                   | 1  | 1  | 1  | 0    | 1     | 1      | 0 | 0   | 1  |

| 17             | 27.165                 | 310         | 17.38              | 37.86                                   | 0  | 1  | 1  | 0    | 1     | 1      | 0 | 0   | 1  |

| 18             | 27.175                 | 309         | 17.39              | 37.87                                   | 1  | 0  | 1  | 0    | 1     | 1      | 0 | 0   | 1  |

| 19             | 27 185                 | 308         | 17.40              | 37.88                                   | 0  | 0  | 1  | 0    | 1     | 1      | 0 | 0   | 1  |

| 20             | 27.205                 | 306         | 17.42              | 37.90                                   | 0  | 1  | 0  | 0    | 1     | 1      | 0 | 0   | 1  |

| 21             | 27.215                 | 305         | 17.43              | 37.91                                   | 1  | 0  | 0  | 0    | 1     | 1      | 0 | 0   | 1  |

| 22             | 27.225                 | 304         | 17.44              | 37.92                                   | 0  | 0  | 0  | 0    | 1     | 1      | 0 | 0   | 1  |

| 23             | 27.255                 | 301         | 17.47              | 37.95                                   | 1  | 0  | 1  | 1    | 0     | 1      | 0 | 0   | 1  |

| 24             | 27.235                 | 303         | 17.45              | 37.93                                   | 1  | 1  | 1  | 1    | 0     | 1      | 0 | 0   | 1  |

| 25             | 27.245                 | 302         | 17.46              | 37.94                                   | 0  | 1  | 1  | 1    | 0     | 1      | 0 | 0   | 1  |

| 26             | 27.265                 | 300         | 17.48              | 37.96                                   | 0  | 0  | 1  | 1    | 0     | 1      | 0 | 0   | 1  |

| 27             | 27.275                 | 299         | 17.49              | 37.97                                   | 1  | 1  | 0  | 1    | 0     | 1      | 0 | 0   | 1  |

| 28             | 27.285                 | 298         | 17.50              | 37.98                                   | 0  | 1  | 0  | 1    | 0     | 1      | 0 | 0   | 1  |

| 29             | 27.295                 | 297         | 17.51              | 37.99                                   | 1  | 0  | 0  | 1    | 0     | 1      | 0 | 0   | 1  |

| 30             | 27.305                 | 296         | 17.52              | 38.00                                   | 0  | 0  | 0  | 1    | 0     | 1      | 0 | 0   | 1  |

| 31             | 27.315                 | 295         | 17.53              | 38.01                                   | 1  | 1  | 1  | 0    | 0     | 1      | 0 | 0   | 1  |

| 32             | 27.325                 | 294         | 17.54              | 38.02                                   | 0  | 1  | 1  | 0    | 0     | 1      | 0 | 0   | 1  |

| 33             | 27.335                 | 293         | 17.55              | 38.03                                   | 1  | 0  | 1  | 0    | 0     | 1      | 0 | 0   | 1  |

| 34             | 27.345                 | 292         | 17.56              | 38.04                                   | 0  | 0  | 1  | 0    | 0     | 1      | 0 | 0   | 1  |

| 35             | 27.355                 | 291         | 17.57              | 38.05                                   | 1  | 1  | 0  | 0    | 0     | 1      | 0 | 0   | 1  |

| 36             | 27.365                 | 290         | 17.58              | 38.06                                   | Ð  | 1  | 0  | 0    | 0     | 1      | 0 | 0   | 1  |

| 37             | 27.375                 | 289         | 17.59              | 38.07                                   | 1  | 0  | 0  | 0    | 0     | 1      | 0 | 0   | 1  |

| 38             | 27.385                 | 288         | 17.60              | 38.08                                   | 0  | 0  | 0  | 0    | 0     | 1      | 0 | 0   | 1  |

| 39             | 27.395                 | 287         | 17.61              | 38 09                                   | 1  | 1  | 1  | 1    | 1     | 0      | 0 | 0   | 1  |

| 40             | 27.405                 | _286        | 17.62              | 38.10                                   | 0  | 1_ | 1  | 1    | 1     | 0      | 0 | 0   | 1_ |

NOTES: 1) HIGH Level ("1") = 4.5 to 5.5 VDC; LOW Level ("0") = GND.

<sup>2)</sup> Pins 7 & 8 permanently wired HIGH & LOW respectively for all 40 channels and are often not even shown in the TRUTH CHART.

<sup>3)</sup> Australian 18 Channel rig frequencies are U.S. Channel 5 to U.S. Channel 22.

called a "Truth Chart".

How exactly was the number "330" decided? Chart 2 shows the truth states for Channel 1 only. Above each PLL program pin are numbers I've labelled "POWERS OF 2", such as 1, 2, 4, 8 up to 256 because this is exactly how a binary counter counts. By adding up the weight or significance of every pin where a "1" appears, the N-Code is determined. (The "0" pins are always ignored.) In this example, we have 256+64+8+2=330. Figure 11 shows the actual voltage switching. Try the math for a few other channels yourself; you'll be using this knowledge eventually!

**CHART 2**

Channel 1 Binary Programming Code of PLL02A AM Synthesizer Described in Text

$\div$  N = 330: 256's bit + 64's bit + 8's bit + 2's bit = 330

| POWERS OF 2       1       2       4       8       16       32       64       128       256         PLL PROGRAM PIN NUMBER       15       14       13       12       11       10       9       8       7         TRUTH STATE, CHANNEL 1       0       1       0       1       0       0       1       0       1 |                           | т  | <del></del> |    | ·  | · · · · · · · · · · · · · · · · · · · |    |    |     |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----|-------------|----|----|---------------------------------------|----|----|-----|-----|

| PLL PROGRAM PIN NUMBER  15 14 13 12 11 10 9 8 7  TRUTH STATE.                                                                                                                                                                                                                                                  | POWERS OF 2               | 1  | 2           | 4  | 8  | 16                                    | 32 | 64 | 128 | 256 |

| TRUTH STATE, CHANNEL 1 0 1 0 0 1 0 1                                                                                                                                                                                                                                                                           | PLL PROGRAM<br>PIN NUMBER | 15 | 14          | 13 | 12 | 11                                    | 10 | 9  |     | 7   |

|                                                                                                                                                                                                                                                                                                                | TRUTH STATE,<br>CHANNEL 1 | 0  | 1           | 0  | 1  | 0                                     | 0  | 1  | 0   | 1   |

<sup>&</sup>quot;1" = +4--8 VDC; "0" = 0 VDC or Ground.

Notice from Chart 1 and Figure 11 that the logic states of pins 7 and 8  $\,$ never change at all for any of the 40 channels. Instead they are permanently hard-wired to the chassis such that Pin 7 is always connected to +DC voltage ("1") and Pin 8 is always grounded ("0").

FIGURE 11. HOW THE BINARY N-CODE IS GENERATED

÷ N = 256 bit + 64 bit + 8 bit + 2 bit = 330 for Channel 1

You'll discover that many service manuals won't even indicate these pin states in their Truth Charts because they never change when programming the legal 40 channels only. This is a case of those missing blanks I'm filling in for you, and you can test this idea by checking the rig's circuit diagram. Compare the total programming pins available to the total number used in a 40-channel rig; you'll find an obvious modification source!

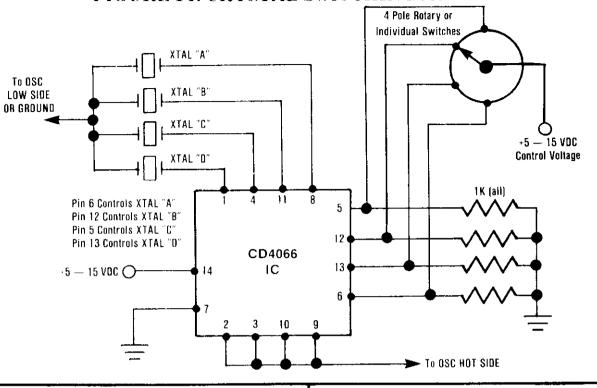

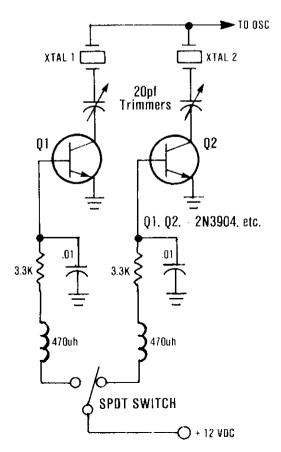

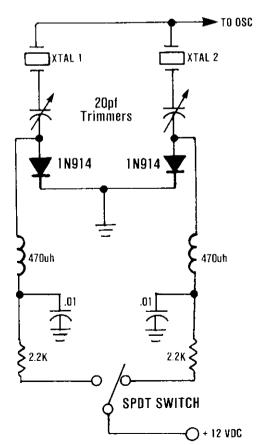

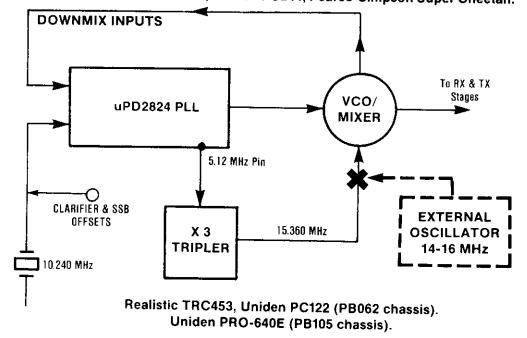

The 18-Channel Australian CB service was recently expanded legally to match the standard 40-Channel FCC American service. Since many Australian rigs are simply U.S. rigs with a different (limited) Channel Selector switch, they can be easily modified to cover the extra channels. For example, Australian Channel 1 is 27.015 MHz, which is U.S. Channel 5. The N-Code here is 325. The N-Code for Australian Ch. 18 (27.225 MHz) is 304. Therefore by reprogramming N-Codes of an 18 channel Australian rig for numbers greater than 325 or less than 304, the rig can be expanded.